[i] Работа с OTP в микроконтроллере К1986ВЕ8Т (12164)

Микроконтроллер К1986ВЕ8Т (с маркировкой на крышке корпуса 12164) - это микроконтроллер с однократно программируемой памятью (OTP). В статье приведены базовые сведения для успешного программирования памяти OTP микроконтроллера К1986ВЕ8Т в среде Keil uVision.

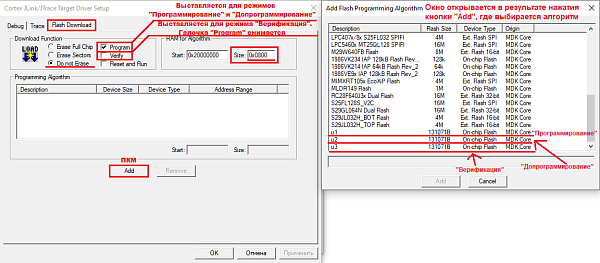

Программирование памяти OTP осуществляется в три этапа, для каждого из них необходим отдельный алгоритм программирования FLM.

- Программирование. Используется алгоритм u1.flm;

- Допрограммирование. Используется алгоритм u2.flm;

- Верификация. Используется алгоритм u3.flm.

Используемые FLM-алгоритмы соответствуют актуальной процедуре программирования (п.7.9.1 "Методика программирования OTP" спецификации ТСКЯ.431296.048СП) и подходят только для микроконтроллеров К1986ВЕ8Т с маркировкой 12164.

FLM-алгоритмы находятся в составе проекта, доступного для загрузки в конце статьи в разделе "Файлы для скачивания". Их необходимо разместить по пути: ./Keil_v5/ARM/Flash (где "Keil_v5" - папка, в которую установлена среда разработки Keil uVision).

Для корректного применения данных FLM-файлов необходимо обеспечить тактирование микроконтроллера от внешнего генератора на 48 МГц, подключенного ко входу микросхемы HSE0_OSC_IN. В алгоритмах FLM в блоке управления тактированием микросхемы эта частота делится на 2, в результате чего формируется частота 24 МГц - это значение близко к максимальной частоте работы OTP (25 МГц, период 40 нс). На этой частоте необходимо проводить верификацию OTP (но в рабочем режиме OTP-память микросхемы на такой частоте функционировать не будет в связи с наличием задержек WaitCycle).

Процесс программирования OTP будет рассмотрен на отладочной плате компании "Миландр" для микроконтроллера К1986ВЕ8Т с адаптером. Адаптер представляет собой отдельную плату, содержащую контактное устройство для микроконтроллера и подключаемую к основной плате, которая имеет все необходимые выходы периферии.

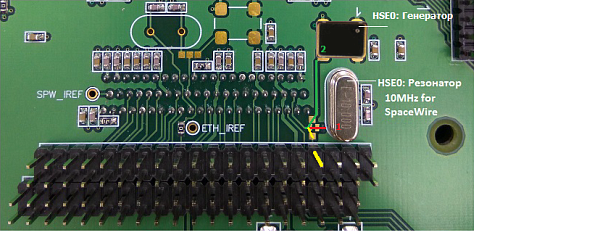

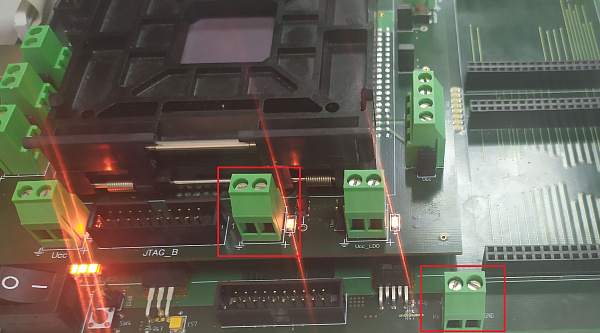

На плате адаптера в качестве источника частоты HSE0 изначально установлен кварцевый резонатор. Резонатор необходимо отключить от вывода HSE0_OSC_IN микросхемы, а на соседнюю посадочную площадку на плате установить генератор на 48 МГц. Вид с обратной стороны платы адаптера с установленным генератором представлен на рисунке 1.

Рисунок 1 - Подключение источников тактирования HSE0 на плате адаптера микроконтроллера К1986ВЕ8Т

Согласно рисунку 1, для подключения генератора необходимо обеспечить соединение "зеленой" дорожки. Это можно сделать, установив резистор номиналом 0 Ом. Дополнительно, чтобы иметь возможность проверить работоспособность генератора (или кварцевого резонатора), можно также соединить "желтую" дорожку. Это позволит проконтролировать работу источника тактирования на выводе, расположенном на обратной стороне основной платы (рисунок 2). В противном случае визуально убедиться в работе генератора, например, с помощью осциллографа, будет невозможно.

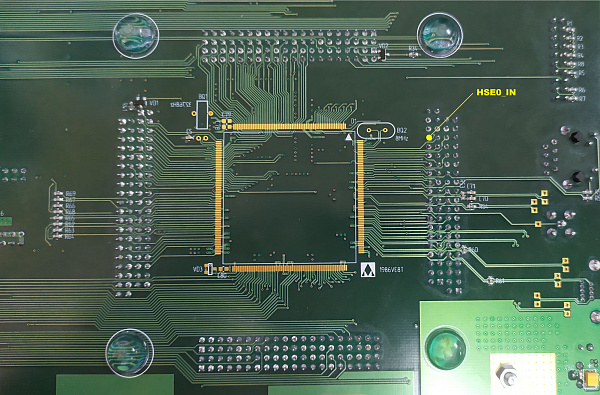

Рисунок 2 - Расположение вывода HSE0_OSC_IN на обратной стороне платы

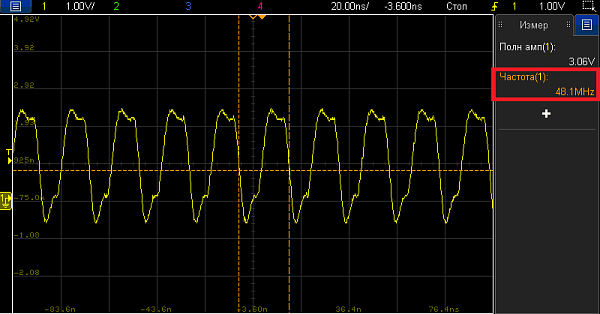

После подачи питания на микроконтроллер работоспособность генератора можно проверить, установив щуп осциллографа на вывод, обозначенный на рисунке 2. При правильной работе генератора осциллограмма сигнала будет аналогично той, что приведена на рисунке 3.

Рисунок 3 - Осциллограмма проверки работы генератора 48 МГц

После этого отладочная плата готова к работе. Для начала рекомендуется запустить проект из раздела "Файлы для скачивания" из ОЗУ микроконтроллера, выставив перед этим на плате режим работы микроконтроллера MODE[7:0] = 00000000 (WAIT BOOT JTAG A). Можно использовать и другие режимы загрузки, но в качестве примера в статье будет использоваться режим WAIT BOOT JTAG A с включенным отладочным интерфейсом JTAG A. Настройки проекта аналогичны описанным в статье "[i] Настройки проекта IDE Keil для МК К1986ВЕ8Т (RAM)". Код программы приведен в фрагменте кода 1, при этом стоит обратить внимание на выделенные фрагменты - на плате используется генератора вместо кварцевого резонатора, что требует иных программных настроек. Этот же код будет использован для записи в OTP. Режим работы микроконтроллера при записи OTP останется прежним.

#include "MDR1986VE8T.h"

#include "spec.h"

#include "mdr32f8_config.h"

#include "mdr32f8_port.h"

#include "mdr32f8_clkctrl.h"

PORT_InitTypeDef PORT_InitStructure;

#define VD7 PORT_Pin_16

#define VD8 PORT_Pin_17

#define VD9 PORT_Pin_18

/*Функция задержки*/

void Delay(__IO uint32_t nCount)

{

for (; nCount != 0; nCount--);

}

int main(void)

{

/* Выключение блока сброса, предназначенного для выработки аппаратного сброса при включении основного питания */

POR_disable();

/* Функция установки регистров блока CLKCTRL по умолчанию */

CLKCTRL_DeInit();

/* Функция конфигурирования частоты HSE0 */

CLKCTRL_HSEconfig(CLKCTRL_HSE0_CLK_BYP);

while(CLKCTRL_HSEstatus(CLKCTRL_HSEn_STAT_HSE0_RDY) != SUCCESS){}

/* Конфигурирование блока умножения тактовой частоты */

//CLKCTRL_CPU_PLLconfig(PLL0, CLKCTRL_PLLn_CLK_SELECT_HSE0div1, 0, 1);//PLLn, SRC, Q, N

// while(CLKCTRL_CPU_PLLstatus(0) != SUCCESS){}

CLKCTRL_MAX_CLKSelection(CLKCTRL_MAX_CLK_HSE0div1);

/* Тактирование порта PORTC */

CLKCTRL_PER0_CLKcmd(CLKCTRL_PER0_CLK_MDR_PORTC_EN, ENABLE);

/* Ключи записи в регистры порта */

KEY_reg_accs();

/* Конфигурация PORTC пинов [16:18] */

PORT_InitStructure.PORT_Pin = (PORT_Pin_16|PORT_Pin_17|PORT_Pin_18);

PORT_InitStructure.PORT_SOE = PORT_SOE_OUT;

PORT_InitStructure.PORT_SANALOG = PORT_SANALOG_DIGITAL;

PORT_InitStructure.PORT_SPD = PORT_SPD_OFF;

PORT_InitStructure.PORT_SPWR = PORT_SPWR_10;

/*Настройка порта исходя из настроек в полях структуры */

PORT_Init(PORTC, &PORT_InitStructure);

/*Основной цикл - "мигание" светодиода */

while (1)

{

PORT_SetBits(PORTC, VD7);

Delay(200000);

PORT_ResetBits(PORTC, VD7);

Delay(200000);

}

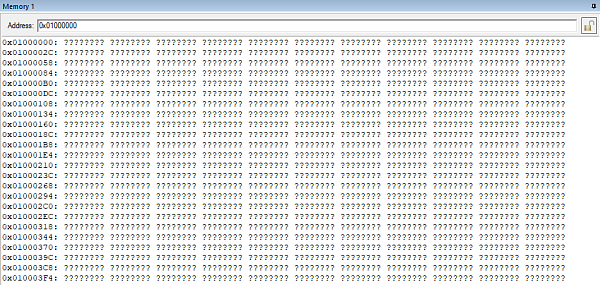

}После запуска режима отладки нужно убедиться, что светодиод мигает. Это означает, что генератор установлен и работает корректно. Перед ответственным этапом программирования OTP рекомендуется выбрать область памяти для записи и проверить ее в окне Memory в режиме отладки. Знаки вопроса по адресам OTP в данном случае означают, что эти ячейки памяти не запрограммированы (для не запрограммированной памяти не записаны значения ECC). Эта ситуация показана на рисунке 4 для адресов, начиная с 0x01000000.

Диапазон адресов OTP:Начало - 0x01000000;

Размер - 0x0001FFFF.

Рисунок 4 - Проверка доступности ячеек памяти OTP в IDE Keil с адреса 0x01000000

Переходя к процедуре программирования памяти OTP, важно обратить внимание, что для программирования битов памяти требуется дополнительный источник напряжения программирования 7.8В. На демонстрационной плате компании "Миландр" предусмотрены два разъема для его подключения (на основной отладочной плате и на плате адаптера), что показано на рисунке 5.

Рисунок 5 - Разъемы для подключения источника напряжения на 7.8В на отладочной плате микроконтроллера К1986ВЕ8Т

Последовательность действий для программирования OTP на отладочной плате:

- Проверить, что выставлен соответствующий режим работы (в качестве примера это режим MODE[7:0] = 00000000 (WAIT BOOT JTAG A)) на основной отладочной плате или на адаптере;

- Проверить, что все перемычки на адаптере с микроконтроллером установлены, за исключением перемычек SHDN и JTAG_EN;

- Подать основное питание микросхемы 3.3В;

- Подать напряжение программирования 7.8В;

- Произвести настройку IDE Keil в соответствии с адресами OTP, куда будет записана программа, и с отладчиком-программатором, используемым для программирования;

- Выбрать в IDE Keil алгоритм u1.flm и нажать опцию Download. Начнётся процесс "Программирование";

- Снять все напряжения питания и программирования: сначала 7.8В, потом 3.3В. Затем повторно подать на микроконтроллер напряжения питания и программирования для дальнейшего допрограммирования, повторно выполнив пункты 3-4.

- Выбрать в IDE Keil алгоритм u2.flm и нажать опцию Download. Начнется процесс "Допрограммирование";

- Снять все напряжения питания и программирования: сначала 7.8В, потом 3.3В. Затем повторно подать на микроконтроллер напряжения питания и программирования для дальнейшей верификации OTP-памяти, повторно выполнив пункты 3-4.

- Выбрать в IDE Keil алгоритм u3.flm и нажать опцию Download. Начнется процесс "Верификация";

- Если процесс "Верификация" прошел неудачно, повторить процессы "Программирование" и "Допрограммирование" один раз с учётом снятия всех напряжений после каждого выполненного этапа. Если после повтора процесс "Верификация" проходит неудачно, то микросхема бракуется (коэффициент программируемости микросхемы NPR составляет не менее 0.7);

- Снять напряжение программирования 7.8В;

- Снять основное питание 3.3В;

После успешного выполнения всех операций, запись памяти OTP завершена.

Более подробно стоит рассмотреть пункт 5, связанный с настройкой среды Keil uVision.

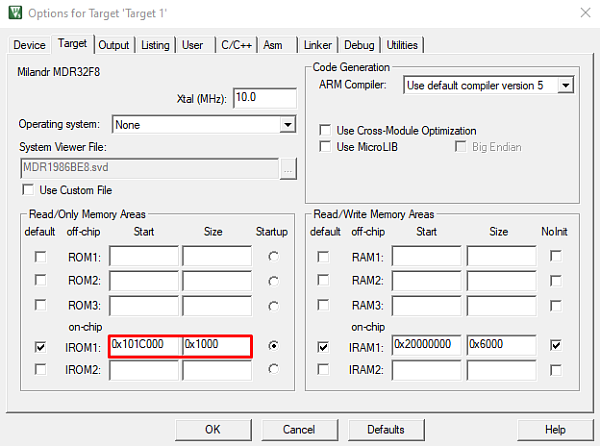

В настройках "Options for Target", во вкладке "Target", настраиваются регионы памяти (начальный адрес и размер региона), под которые собирается программа. В качестве примера для записываемого тестового проекта взят адрес 0x101C000 размером 0x1000. Код тестового проекта гарантированно помещается в этот диапазон памяти. Для собственной программы необходимо указать значение Size для IROM1, равное сумме компонентов Code, RO-data и RW-data (эти данные можно посмотреть в .map файле или в окне "Build Output" после сборки проекта). Настройка вкладки "Target" представлена на рисунке 6.

Рисунок 6 - Настройка вкладки "Target" в IDE Keil

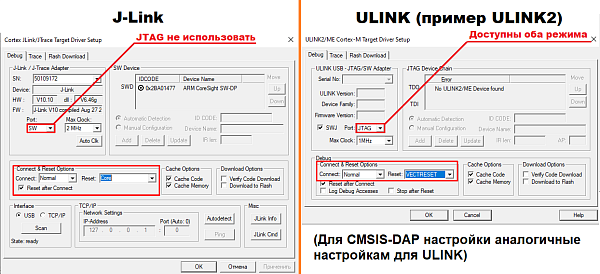

Далее во вкладке "Debug" необходимо выбрать отладчик-программатор. Для корректного программирования OTP требуются определенные настройки в "Settings" > "Debug" (рисунок 7) для программаторов J-Link и ULINK, а также CMSIS-DAP (универсальный программатор для микросхем с ядром CORTEX-M и архитектурой RISC ТСКЯ.468998.109). Настройки для программатора CMSIS-DAP аналогичны настройкам для программатора ULINK.

Рисунок 7 - Настройки отладчиков J-Link, ULINK и CMSIS-DAP в IDE Keil uVision

Настройки программаторов:

- J-Link: допускается работа только в режиме SW. Во вкладке "Debug" в настройках "Connect & Reset Options" установить: Connect - Normal; Reset - Core.

- ULINK и CMSIS-DAP: допускается работа в режимах SW и JTAG. Во вкладке "Debug" в настройках "Connect & Reset Options" установить: Connect - Normal; Reset - VECTRESET.

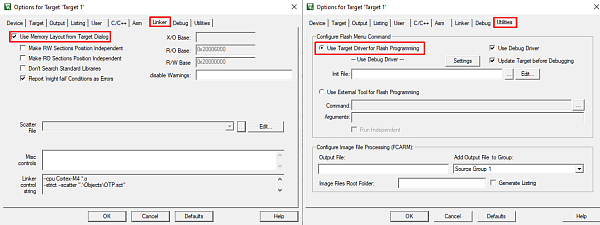

Вкладки окна "Options for Target", "Linker" и "Utilities", должны быть настроены для работы с внутренней памятью. Важные настройки этих вкладок отмечены на рисунке 8.

Рисунок 8 - Настройки вкладок "Linker" и "Utilities" в IDE Keil

Далее - более подробно про пункты 6, 8 и 10 из последовательности действий для программирования OTP на отладочной плате. Раздел выбора FLM находится по пути "Options for Target" > Debug > Settings > Flash Download. Все важные настройки приведены на рисунке 9. Для процессов "Программирование" и "Допрограммирование" должна быть активна только галочка "Program" (галочки "Verify" и "Reset and Run" должны быть сняты). Для процесса "Верификация" должна быть активна только галочка "Verify".

Рисунок 9 - Настройки вкладки "Flash Download" в IDE Keil

После этого отладочная плата и IDE Keil готовы к программированию OTP.

В качестве дополнительной проверки перед запуском можно выполнить следующее: Не подавая питание программирования 7.8В, но выставив все необходимые настройки для программирования, начать программирование OTP. Полоска прогресса в IDE Keil будет двигаться, но сама запись происходить не будет. После этой проверки можно производить фактическую запись с использованием внешнего источника.

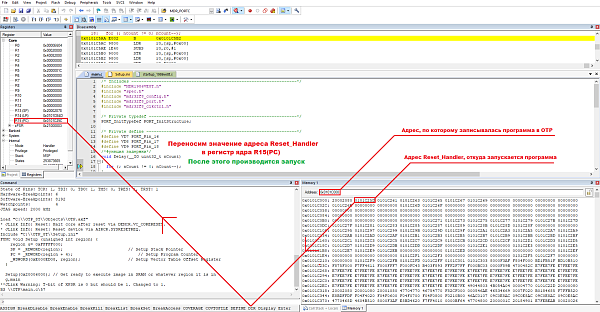

После успешной записи (в старшие адреса OTP-памяти) для проверки исполнения программы из OTP проще всего запустить тот же проект из ОЗУ. В режиме отладки во вкладке Memory по адресу 0x0101C000 уже будет видна записанная программа (см. настройку пункта 5). Чтобы запустить программу непосредственно из OTP, нужно скопировать адрес Reset_Handler (точка входа программы), и записать его в регистр ядра R15(PC). После успешной записи будет виден результат работы программы, записанной в OTP. Последовательность действий показана на рисунке 10.

Рисунок 10 - Запуск программы, записанной в OTP не с нулевого адреса, в IDE Keil uVision

Сохранить статью в PDF