Центра проектирования интегральных микросхем

|

Информационный портал технической поддержки Центра проектирования интегральных микросхем |

DMA (Direct Memory Access) - это специализированный контроллер, предназначенный для пересылки данных без использования ядра микроконтроллера. Данный контроллер применяется в большинстве микроконтроллеров компании "Миландр". Использование DMA позволяет не тратить процессорное время на отслеживание готовности данных в периферийных блоках и их последующую пересылку. Ядро инициализирует DMA и переходит к выполнению других задач, пока не возникнет прерывание от DMA, сигнализирующее о том, что заданное количество данных было передано.

В контроллере DMA реализовано 32 канала, каждый из которых может выполнять свою задачу. При наличии нескольких активных каналов они работают последовательно, выбор канала осуществляется на основе программируемого приоритета и номера канала. Каждый канал за цикл может осуществить от 1 до 1024 передач. Каждому номеру канала соответствует событие (программный запрос или запрос от периферийного блока), по которому инициируется передача.

Например, с помощью контроллера DMA можно передавать массив данных из регистра данных АЦП в массив в ОЗУ, не требуя от ядра отслеживания окончания преобразования АЦП (т.е. готовности данных). В отличие от простого непрерывного копирования, при считывании измерений с АЦП данные нужно читать только по событию их готовности, так как преобразование занимает время. Затем, когда DMA завершит передачу заданного количества данных (цикл DMA), будет сформировано прерывание (сигнализирующее о завершении работы канала), и ядро сможет обработать весь полученный от АЦП массив данных.

Другой пример - передача данных по событию от таймера из заранее сформированного массива в регистр данных ЦАП. Это позволяет с помощью DMA организовать равномерный вывод сигнала на ЦАП. Форма выходного сигнала в этом случае описывается массивом, который указывается в качестве источника данных для DMA. Размер массива задаётся параметром "количество передаваемых данных". По окончании передачи массива возникает прерывание от DMA, указывающее на завершение цикла DMA.

Как и при любой пересылке данных, для запуска обмена с использованием DMA необходимо задать следующие параметры:

После передачи очередной порции данных адреса источника и приемника данных могут либо инкрементироваться, либо оставаться фиксированными.

Поддерживаются следующие типы передач:

Разрядности данных приемника и передатчика должны быть равны и могут быть:

Контроллер DMA состоит из 3 функциональных блоков:

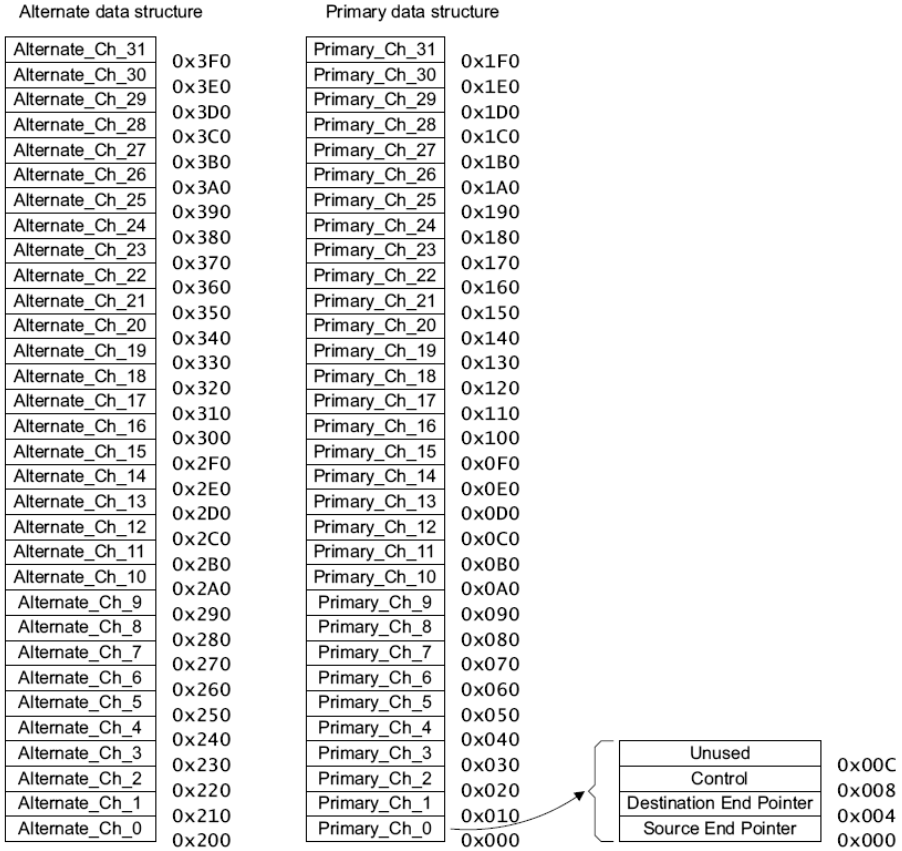

Каждому каналу DMA соответствуют определенные настройки. Эти настройки хранятся в структуре управляющих данных, которая состоит из 4-х 32-битных полей. Все структуры для всех каналов образуют таблицу. Для каждого канала существуют две структуры управляющих данных: первичная и опциональная альтернативная. Использование альтернативной структуры зависит от программных настроек и выбранного режима работы.

Структура (как основная, так и альтернативная) состоят из следующих слов:

Параметры цикла DMA канала находятся в слове Control. Это слово изменяется в процессе работы канала, и по нему можно определить, сколько данных осталось передать и завершен ли цикл.

Слово Control содержит следующие поля:

При начале обработки канала (в начале цикла DMA или блока из 2R передач) контроллер DMA читает конечные адреса источника и приемника данных и управляющее слово Control/channel_cfg.

Контроллер DMA вычисляет адрес текущей передачи из конечного адреса по формуле:

Addr = data_end_ptr - (n_minus_1 << src_inc), где src_inc - инкремент данных источника

После выполнения 2R или N передач контроллер сохраняет обновленное значение channel_cfg в системную память.

Все структуры управляющих данных каналов расположены в условной таблице последовательно: сначала 32 основных структуры для каналов с 0 по 31, затем, если используются, 32 альтернативные структуры для каналов с 0 по 31. Аппаратно реализована работа со всеми 32 каналами, поэтому "сжать" таблицу (например, разместить структуру для канала 5 по относительному адресу 0x00 вместо 0x50, если каналы 0-4 не используются в ПО) невозможно.

Базовый адрес таблицы должен быть кратен общему размеру структуры управляющих данных канала.

Контроллер не содержит внутреннюю память для хранения управляющих данных каналов. Таблица структур представляет собой массив данных в адресном пространстве микроконтроллера, к которому контроллер DMA обращается для чтения адресов и чтения/записи управляющих данных. Поэтому таблица должна располагаться в памяти, доступной контроллеру DMA для чтения и записи.

Если разместить таблицу в Flash-памяти или памяти OTP, контроллер DMA не сможет обновлять поле Control и работать корректно.

Если таблица расположена в ОЗУ, к которому у DMA нет доступа, контроллер также не будет работать. Например, DMA не имеет доступа к памяти DTCM SRAM в микросхемах К1986ВЕ1x (доступна только ядру), и размещение таблицы там приведёт к сбоям (расположение данных в доступной контроллеру DMA области ОЗУ описано в статье "[i] Расположение функций в ОЗУ в IDE Keil"). Аналогично для микросхем К1986ВК025 и памяти TCMA/TCMB RAM. В то же время, в микросхемах MDR1206(A)FI, MDR1215LGI доступ к TCM RAM возможен благодаря наличию в ядре арбитра внешнего доступа к этим блокам по шине AHB.

Контроллеру DMA необходимо указать начальный адрес таблицы структур. Для этого используются регистры:

Достаточно записать адрес в CTRL_BASE_PTR; значение в регистре ALT_CTRL_BASE_PTR установится аппаратно на основе значения CTRL_BASE_PTR.

Периферийные блоки могут запрашивать блочные и одиночные передачи от каналов, используя внутренние сигналы dma_req[С] и dma_sreq[С]. С - номер канала, то есть каждый канал имеет отдельные сигналы от периферии. Передача одного значения называется одиночной передачей, а передача 2R_power данных - блочной передачей.

Обработку одиночных запросов от dma_sreq[C] можно отключать/включать с помощью регистров CHNL_USEBURST_SET / CHNL_USEBURST_CLR. При отключенной обработке одиночных запросов dma_sreq[C] будут обрабатываться только запросы dma_req[C].

В большинстве микроконтроллеров сигналы dma_req[С] и dma_sreq[С] от определенных периферийных контроллеров жестко привязаны к номерам каналов DMA. Но есть версии контроллера DMA с разделением на "реальные" и "виртуальные" каналы (вследствие большого количества источников запросов). Виртуальные каналы содержат только запросы от периферийных блоков и их может быть больше 32. Реальных каналов со структурами управляющих данных остается 32, и виртуальные каналы назначаются на реальные, тем самым подключая источники запросов от периферийных блоков к каналам контроллера DMA. Версию контроллера с виртуальными каналами можно определить по наличию регистров назначения номера виртуального канала на реальный (CHMUX[x]). Такой контроллер DMA есть в микросхемах К1986ВЕ8Т и К1986ВК01x.

Некоторые периферийные блоки могут выставить запросы к DMA сразу после включения микроконтроллера. Если канал DMA, к которому поступил запрос, выключен, то контроллер DMA оповестит ядро, установив запрос прерывания (см. правила осуществления DMA передач при "запрещенных" каналах в спецификации микросхем, правило №19). Сигнал dma_done[C] устанавливается в логическую "1" и фиксируется в этом состоянии. Таким образом DMA информирует о запросах от периферии, поступивших на неактивные каналы. В большинстве микросхем сигналы dma_done[C] от всех каналов объединены в один общий, поэтому идентифицировать какой-либо другой работающий канал не удастся. Если данный механизм оповещения не требуется, то его можно отключить. Для этого необходимо:

Каналы DMA осуществляют пересылку данных последовательно. В один момент времени передачи может осуществлять только один канал.

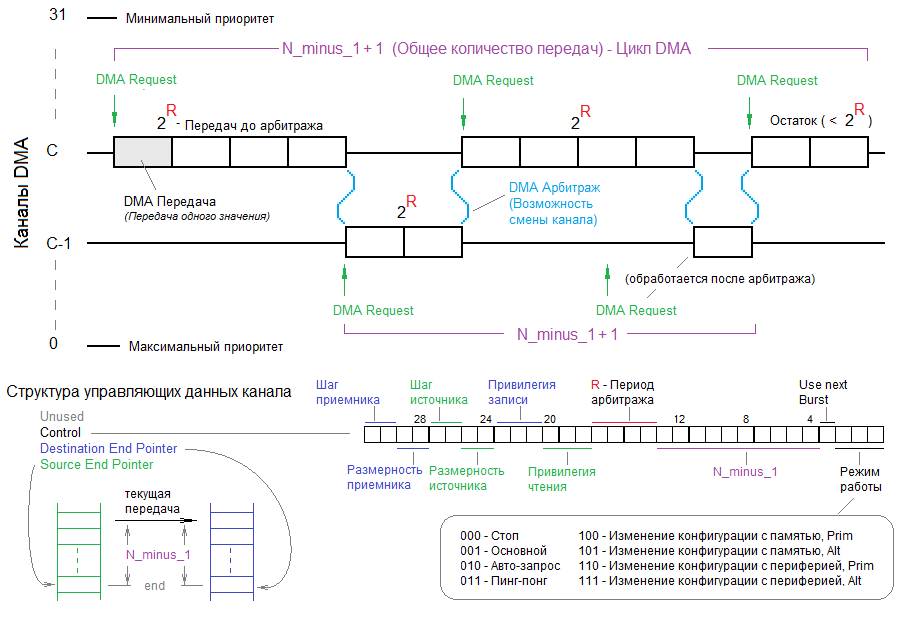

"Одновременное" исполнение нескольких задач (работа нескольких каналов) обеспечивается за счет арбитража активных каналов и попеременного осуществления передач каналами. В настройках каждого канала количество передач до арбитража задает параметр R_power. Количество передач до арбитража может быть задано меньшим, чем полный цикл обмена канала DMA. Значение этого параметра является степенью 2, т.е. возможны 1, 2, 4, 8, 16, 32, 64, 128, 256, 512 и 1024 непрерывные передачи, которые не могут быть прерваны процедурой арбитража.

Например, необходимо передать 100 значений из массива в массив. Если установить R_power = 6, то контроллер DMA выполняет передачи активного канала до осуществления 64 (26) передач. Затем выполняется процедура арбитража:

Канал с номером 0 имеет наивысший приоритет по умолчанию. Приоритет снижается с увеличением номера канала. При выборе значения R_power необходимо учитывать, что слишком большое значение ускорит обработку одного канала, но может ухудшить отзывчивость системы на запросы других каналов.

На рисунке 2 показана структурная схема работы каналов DMA с осуществлением арбитража.

Пояснения к рисунку 2:

В контроллере DMA реализованы следующие типы циклов:

После окончания цикла DMA контроллер устанавливает тип цикла в недействительный режим для предотвращения повтора выполненного цикла DMA.

При поступлении запроса (программного или от периферийного блока) к выключенному каналу (канал выключается после завершения работы) контроллер DMA выставит запрос прерывания.

Контроллер работает только с основной или альтернативной (в зависимости от программных настроек) структурой управляющих данных канала. После разрешения работы канала и получения запроса цикл DMA выглядит следующим образом:

1) Контроллер выполняет 2R передач и обновляет число передач в цикле DMA в слове channel_cfg. Если число оставшихся передач равно 0, контроллер переходит к шагу 3, иначе - к шагу 2.

2) Осуществление арбитража:

3) Контроллер устанавливает dma_done[C] в состояние "1" на один такт сигнала hclk. Это указывает процессору на завершение цикла DMA. Режим работы в слове channel_cfg обновляется на "стоп".

Может использоваться для передачи большого количества данных по однократному запросу. Цикл DMA в данном режиме аналогичен циклу DMA в основном режиме, за исключением того, что на этапе 2 контроллер автоматически формирует новый запрос на обработку для текущего канала, если он становится самым приоритетным в ходе арбитража. Это позволяет продолжить передачу без необходимости получения внешних запросов.

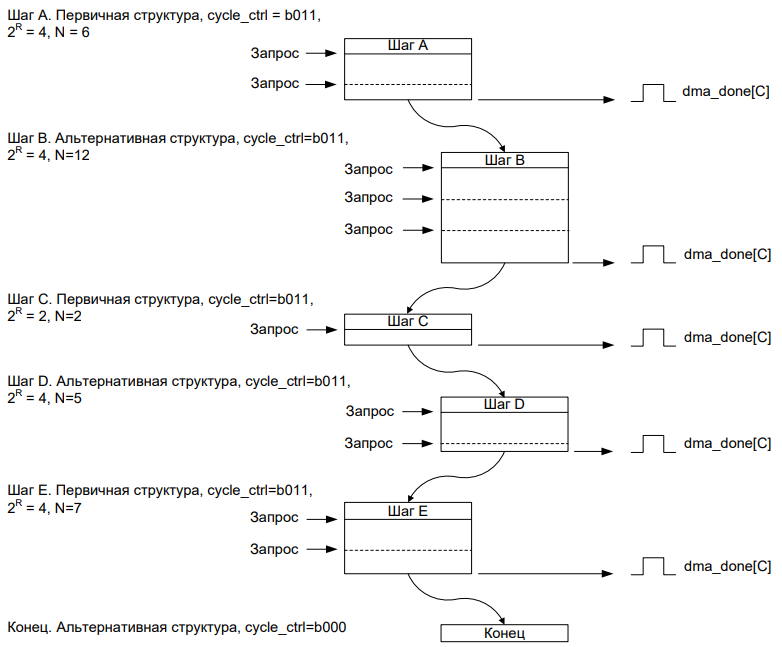

Контроллер выполняет циклы DMA как в основном режиме, но попеременно используя основную и альтернативную структуры (сначала одну, потом, после завершения с ней цикла, другую) до тех пор, пока не считает структуру с режимом "стоп", после чего запретит работу канала. После завершения цикла с каждой структурой контроллер выставляет dma_done[С] - по этому сигналу (по прерыванию) можно обновить режим работы и число передач в цикле DMA в отработавшей структуре, пока контроллер работает со второй структурой.

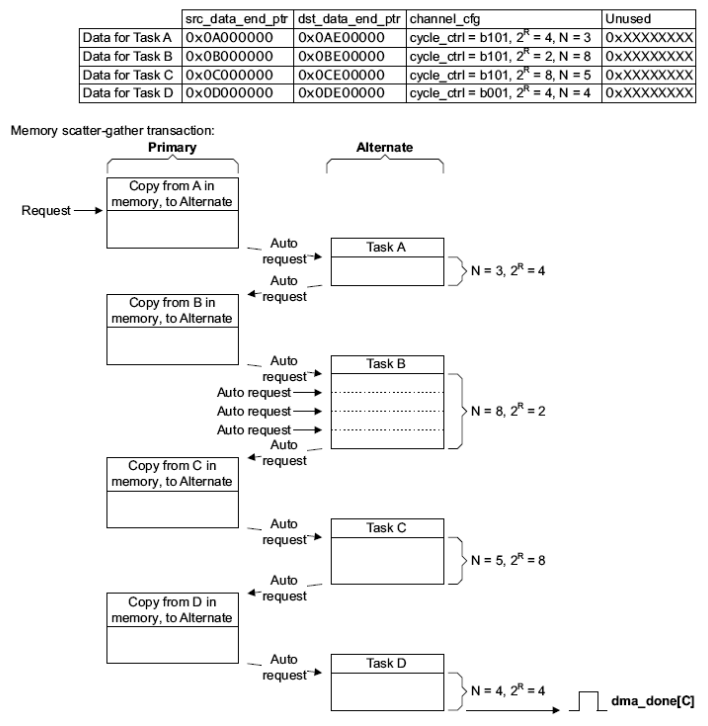

Данный режим, как и авто-запрос, предназначен для передачи больших объемов данных (и в целом функционирует аналогично), но позволяет выполнить последовательность из нескольких разных задач.

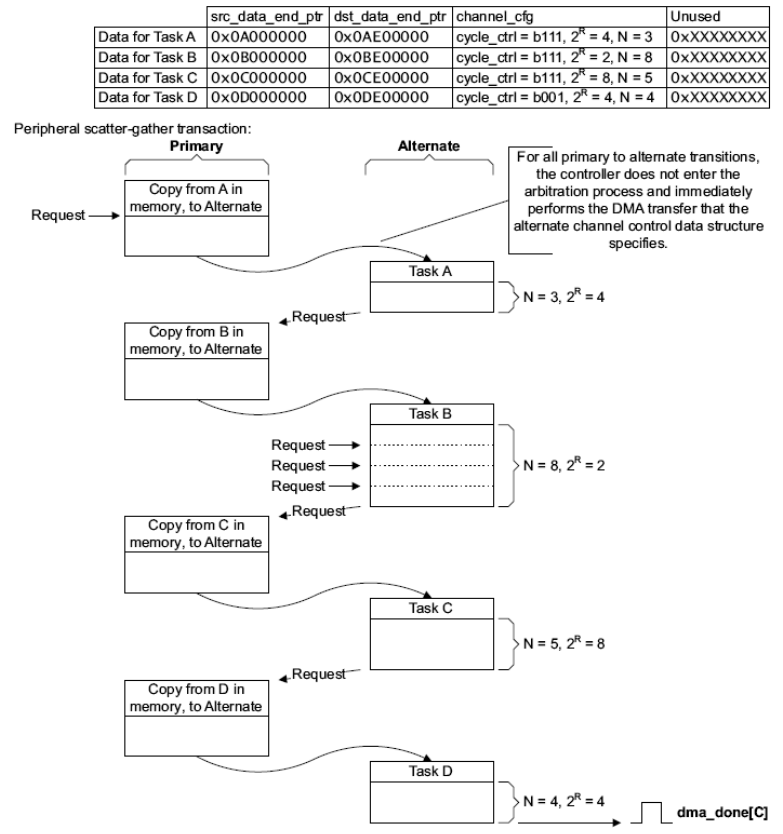

Контроллер, получив начальный запрос на обработку, выполняет 4 передачи DMA, используя первичную структуру управляющих данных. Эти 4 передачи копируют новую задачу (структуру из 4 слов, аналогичную структуре канала) из памяти в альтернативную структуру управляющих данных. Затем осуществляется арбитраж, формируется авто-запрос, и контроллер начинает цикл DMA, используя уже альтернативную структуру (т.е. выполняет саму задачу). После завершения работы процесс повторяется: контроллер снова использует первичную структуру для копирования следующей задачи в альтернативную. Контроллер продолжает выполнять циклы DMA, меняя структуры управляющих данных, пока не произойдет одно из следующих условий:

После исполнения контроллером всех запланированных передач с использованием первичной структуры он делает эти управляющие данные "неправильными" путем установки cycle_ctrl в 3'b000.

Контроллер устанавливает флаг dma_done[C] в этом режиме только тогда, когда передача завершается с использованием основного цикла (после выполнения последней альтернативной задачи).

Режим аналогичен режиму "исполнение с изменением конфигурации", но вместо авто-запросов при исполнении альтернативной структуры - обычные запросы (что позволяет работать с периферийными блоками), и при переключении с выполнения первичной структуры (копирование задачи) на выполнение альтернативной структуры арбитраж не производится. Это позволяет выполнить несколько последовательных задач, связанных с периферией, с минимальными задержками.

| Сайт: | https://support.milandr.ru |

| E-mail: | support@milandr.ru |

| Телефон: | +7 495 221-13-55 |