[i] Запуск МК К1986ВЕ8Т в режимах EXTBUS_8_ECC и EXTBUS_CFG

После включения питания или после любого сигнала сброса МК К1986ВЕ8Т начинает выполнять загрузочную программу, которая по состоянию выводов MODE[7:0] (PE[31:24]) определяет, в каком из режимов будет функционировать МК. Полный список режимов работы МК приведён в спецификации, пункт «Режимы работы микроконтроллера». В данной статье будут рассмотрены режимы запуска МК из внешней памяти: EXTBUS_8_ECC и EXTBUS_CFG.

Содержание

1. Режимы запуска МК из внешней памяти

В составе МК реализован контроллер внешней шины (EXTBUSCNTR), который позволяет выполнять программу непосредственно из внешней памяти, т.е. позволяет микроконтроллеру работать в режиме микропроцессора. В загрузочной программе для этого предназначены 4 режима работы, приведённые в таблице 1.

Таблица 1 - Режимы работы МК для выполнения программы из внешней памяти|

Биты ЕСС MODE[7:4] |

Биты режима MODE[3:0] |

Режим |

Краткое описание |

|

1100 |

0011 |

EXTBUS_8_ECC+JB |

Запуск из внешней памяти с (0x1000_0000), сконфигурированной в минимальный режим: - шина данных D[7:0] ( {PE[5:0], PD[31:30]} ); - шина адреса A[15:0] ( {PD[13:0], PC[31:30]} ); - сигнал OEn[0] ( PD[23] ) c последовательной организацией ECC с базового адреса 0x1000_9000 с включенным интерфейсом отладки через выводы JTAG_B. |

|

1101 |

0100 |

EXTBUS_8_ECC+JA |

Запуск из внешней памяти с (0x1000_0000), сконфигурированной в минимальный режим: - шина данных D[7:0] ( {PE[5:0], PD[31:30]} ); - шина адреса A[15:0] ( {PD[13:0], PC[31:30]} ); - сигнал OEn[0] ( PD[23] ) с последовательной организацией ECC с базового адреса 0x1000_9000 с включенным интерфейсом отладки через выводы JTAG_A.

|

|

1010 |

0101 |

EXTBUS_CFG+JB |

Запуск из внешней памяти с (0x1000_0000) c чтением конфигурации в режиме: - шина данных D[7:0] ( {PE[5:0], PD[31:30]} ); - шина адреса A[10:3] ( {PD[8:1]} ); - сигнал OEn[0] ( PD[23] ).

Читается DATA[7:0] = {ECC[3:0], CFGx[3:0]}, где: - CFG0 = Режим запуска (8, 16, 32, 64); - CFG1 = Режим ЕСС (нет, послед., параллельн.); - CFG2 = ECCBASE[3:0]; - CFG3 = ECCBASE[7:4]; … - CFG9 = ECCBASE[31:28] с включенным интерфейсом отладки через выводы JTAG_B.

|

|

0110 |

0110 |

EXTBUS_CFG+JA |

Запуск из внешней памяти с (0x1000_0000) c чтением конфигурации в режиме: - шина данных D[7:0] ( {PE[5:0], PD[31:30]} ); - шина адреса A[10:3] ( {PD[8:1]} ); - сигнал OEn[0] ( PD[23] ).

Читается DATA[7:0] = {ECC[3:0], CFGx[3:0]}, где: - CFG0 = Режим запуска (8, 16, 32, 64); - CFG1 = Режим ЕСС (нет, послед., параллельн.); - CFG2 = ECCBASE[3:0]; - CFG3 = ECCBASE[7:4]; … - CFG9 = ECCBASE[31:28] с включенным интерфейсом отладки через выводы JTAG_A.

|

Дополнение в конце названия режимов EXTBUS_8_ECC и EXTBUS_CFG: «+JA» или «+JB» определяет, через какие выводы: JTAG_A или JTAG_B будет доступен интерфейс отладки.

Описание запуска отладки в режимах EXTBUS_8_ECC и EXTBUS_CFG в среде Keil приведено в статье «[i] Настройка проекта в IDE Keil для запуска К1986ВЕ8Т из внешней ОЗУ К1645РУ5У на отладочной плате».

2. Режим работы EXTBUS_8_ECC+JA(JB)

Режим работы EXTBUS_8_ECC+JA(JB) используется для старта МК из внешней 8-разрядной памяти с использованием последовательного режима ECC.

В данном режиме работы загрузочная программа выполняет настройку контроллера внешней шины и портов ввода-вывода для работы с внешней 8-разрядной памятью.

В контроллере внешней шины настраивается регион 0 (0x1000_0000 - 0x17FF_FFFF) в режим работы с использованием 8-разрядной шины данных D[7:0] и проверкой ECC по коду Хэмминга (72, 64). Сигнал готовности READY и синхросигнал OCLK не используются. Проверочные биты ECC располагаются последовательно в самой памяти (последовательная организация ECC), начиная с базового адреса 0x1000_9000.

Временные параметры транзакции на шине устанавливаются в следующие значения: WS_HOLD[3:0] = 0x4, WS_SETUP[3:0] = 0x4, WS_ACTIVE[7:0] = 0x7F. При необходимости временные параметры могут быть изменены в ходе выполнения программы, подробнее об этом описано в пункте «4. Изменение параметров работы внешней шины».

В контроллере портов ввода-вывода настраивается минимальный набор выводов МК для работы с внешней памятью:

- шина данных D[7:0] ( {PE[5:0], PD[31:30]} );

- шина адреса A[15:0] ( {PD[13:0], PC[31:30]} );

- сигнал чтения данных OEn[0] ( PD[23] ).

Остальные выводы портов ввода-вывода МК, например, сигналы управления CSn[0], CS[0] (разрешение региона) и WEn[0] (запись данных), сигналы шины адреса A[31:16], не инициализируются и находятся по сбросу в режиме аналоговой функции в высокоимпедансном состоянии. Входы микросхемы памяти, которые не подключены к набору выводов МК, инициализируемых загрузочной программой, должны быть доопределены на плате до допустимых логических уровней напряжения с помощью резисторов доопределения.

Так как сигнал чтения данных OEn[0] при запуске МК до конфигурирования находится в высокоимпедансном состоянии, то рекомендуется доопределить сигнал OEn[0] до уровня логической единицы с помощью резистора доопределения во избежание наводок, которые могут привести к ложной выдаче данных микросхемой памяти.

Загрузочная программа конфигурирует только минимальный набор внешней шины, чтобы не ограничивать использование других выводов МК. При необходимости требуемые сигналы внешней шины могут быть сконфигурированы в программе после запуска МК. Подключение микросхемы памяти к МК в режиме EXTBUS_8_ECC+JA(JB) приведено в пункте «5. Подключение внешней памяти к МК».

После окончания инициализации контроллера внешней шины и контроллера портов ввода-вывода загрузочная программа выполняет следующие действия:

- устанавливает адрес указателя стека в значение, считанное из ячейки с адресом 0x1000_0000 (SP);

- устанавливает адрес таблицы векторов в значение 0x1000_0000 (VTOR);

- осуществляет безусловный переход по адресу, считанному из ячейки 0x1000_0004 (RESET_HANDLER).

При выполнении загрузочной программы в специальную структуру, которая располагается в ОЗУ по адресу 0x2000_7FF0, записывается информация об ошибках, которые возникли в процессе загрузки.

3. Режим работы EXTBUS_CFG+JA(JB)

Режим работы EXTBUS_CFG+JA(JB) используется для старта МК из внешней памяти, при этом разрядность шины данных (8, 16, 32, 64) и режим ECC (без ECC, последовательный, параллельный) определяются значениями конфигурационных данных CFGx, которые МК считывает в процессе инициализации из внешней памяти по адресам 0x1000_0400, 0x1000_0408, … 0x1000_0448.

В данном режиме работы загрузочная программа выполняет настройку контроллера внешней шины и портов ввода-вывода в два этапа:

1) первоначальная инициализация для считывания конфигурационных значений CFGx;

2) итоговая инициализация в зависимости от считанных конфигурационных значений CFGx.

3.1 Первоначальная инициализация

При первоначальной инициализации загрузочная программа настраивает в контроллере внешней шины регион 0 (0x1000_0000 - 0x17FF_FFFF) для работы с использованием 8-разрядной шины данных D[7:0]. Аппаратная проверка ECC по коду Хэмминга (72, 64), а также сигнал готовности READY и синхросигнал OCLK не используются. Временные параметры транзакции на шине устанавливаются в следующие значения: WS_HOLD[3:0] = 0x4, WS_SETUP[3:0] = 0x4, WS_ACTIVE[7:0] = 0x7F.

В контроллере портов ввода-вывода настраивается минимальный набор выводов МК для работы с внешней памятью:

- шина данных D[7:0] ( {PE[5:0], PD[31:30]} );

- шина адреса A[10:3] ( {PD[8:1]} );

- сигнал OEn[0] ( PD[23] );

- сигнал WEn[0] ( PD[24] ).

Остальные выводы портов ввода-вывода МК, например, сигналы управления CSn[0], CS[0] (разрешение региона) и WEn[0] (запись данных), сигналы шины адреса A[31:11] и A[2:0], не инициализируются и находятся по сбросу в режиме аналоговой функции в высокоимпедансном состоянии. Входы микросхемы памяти, которые не подключены к набору выводов МК, инициализируемых загрузочной программой, должны быть доопределены на плате до допустимых логических уровней напряжения с помощью резисторов доопределения.

Так как сигнал чтения данных OEn[0] при запуске МК до конфигурирования находится в высокоимпедансном состоянии, то рекомендуется доопределить сигнал OEn[0] до уровня логической единицы с помощью резистора доопределения во избежание наводок, которые могут привести к ложной выдаче данных микросхемой памяти.

Загрузочная программа конфигурирует только минимальный набор внешней шины, чтобы не ограничивать использование других выводов МК. При необходимости требуемые сигналы внешней шины могут быть сконфигурированы в программе после запуска МК. Подключение микросхемы памяти к МК в режиме EXTBUS_CFG+JA(JB) приведено в пункте «5. Подключение внешней памяти к МК».

После настройки контроллера внешней шины и портов ввода-вывода из ячеек памяти по адресам 0x1000_0400, 0x1000_0408, … 0x1000_0448 считываются конфигурационные значения с ECC: DATA[7:0] = {ECC[3:0], CFGx[3:0]}, после чего выполняется программный контроль ЕСС. При обнаружении одиночной ошибки загрузочная программа исправляет её, при обнаружении двойной ошибки - формирует программный сигнал сброса, и МК заново начинает выполнение загрузочной программы.

3.2 Итоговая инициализация

В зависимости от считанных конфигурационных значений CFGx загрузочная программа выполняет итоговую инициализацию контроллера внешней шины и портов ввода-вывода. Конфигурационные значения CFGx имеют следующее назначение:

CFG0 - разрядность шины данных:

- CFG0 = 1 - 8-ми битная шина;

- CFG0 = 2 - 16-ти битная шина;

- CFG0 = 3 - 32-x битная шина;

- CFG0 = 4 - 64-x битная шина.

CFG1 - режим ЕСС:

- CFG1 = 1 - без проверки ECC.

- CFG1 = 2 - последовательная организация ECC. При последовательной организации проверочные биты ECC располагаются непосредственно в самой памяти, начиная с базового адреса расположения ECC. Базовый адрес ECC задаётся значениями CFG9-CFG2.

- CFG1 = 3 - параллельная организация ECC. Допускается только для 32-х и 64-х разрядной шины данных. При параллельной организации проверочные биты ECC располагаются в дополнительных разрядах шины данных: 32 данные + 8 ECC, 64 данные + 16 ECC.

В контроллере внешней шины для работы с памятью настраивается регион 0 (0x1000_0000 - 0x17FF_FFFF). В зависимости от значений CFG9-CFG0 устанавливается разрядность шины данных и режим ECC. Сигнал готовности READY, синхросигнал OCLK и кэширование данных не используются.

Временные параметры транзакции на шине устанавливаются в следующие значения: WS_HOLD[3:0] = 0x4, WS_SETUP[3:0] = 0x4, WS_ACTIVE[7:0] = 0x7F. При необходимости временные параметры могут быть изменены в ходе выполнения программы, подробнее об этом описано в пункте «4. Изменение параметров работы внешней шины».

В контроллере портов ввода-вывода настраивается набор выводов МК для работы с внешней памятью:

- шина адреса A[20:0] ( {PD[18:0], PC[31:30]} );

- сигнал OEn[0] ( PD[23] ).

В зависимости от значения CFG0 настраивается шина данных:

CFG0 = 1 - 8-ми битная шина D[7:0] ( {PE[5:0], PD[31:30]} );

CFG0 = 2 - 16-ти битная шина D[15:0] ( {PE[13:0], PD[31:30]} );

CFG0 = 3 - 32-х битная шина D[31:0] ( {PB[11:26], PE[13:0], PD[31:30]} );

CFG0 = 4 - 64-х битная шина D[63:0] ( {PA[19:31], PB[0:2], PA[5:0], PE[31:22], PB[11:26], PE[13:0], PD[31:30]} ).

- в REV1-REV4 МК 1986ВЕ8Т и REV1-REV1.1 МК 1986ВЕ81Т загрузочная программа изменяет активный интерфейс отладки с JTAG_A (PA[4:0]) на JTAG_B (PB[8:4]), устанавливая бит MODE[0] в регистрах REG_60_TMRx;

- в REV5 МК 1986ВЕ8Т и REV2 МК 1986ВЕ81Т загрузочная программа отключает интерфейсы JTAG_A и JTAG_B путём установки бита DISABLE_JTAG в регистрах REG_60_TMRx.

CFG0 = 1,2 - недопустимый режим работы;

CFG0 = 3 - 8-ми разрядная шина ECC: D[71:64] ( PE[21:14] );

CFG0 = 4 - 16-ти разрядная шина ECC: D[79:64] ( {PB[3:10], PE[21:14]} ).

После окончания инициализации контроллера внешней шины и контроллера портов ввода-вывода загрузочная программа выполняет следующие действия:

- устанавливает адрес указателя стека в значение, считанное из ячейки с адресом 0x1000_0000 (SP);

- устанавливает адрес таблицы векторов в значение 0x1000_0000 (VTOR);

- осуществляет безусловный переход по адресу, считанному из ячейки 0x1000_0004 (RESET_HANDLER).

При выполнении загрузочной программы в специальную структуру, которая располагается в ОЗУ по адресу 0x2000_7FF0, записывается информация об ошибках, которые возникли в процессе загрузки.

3.3 Размещение конфигурационных значений CFGx в проекте

Для МК программа во внешней памяти располагается, начиная с адреса 0x1000_0000, поэтому в среде разработки область памяти программ (ROM) должна также начинаться с адреса 0x1000_0000.Конфигурационные значения CFGx защищаются ECC и записываются в памяти в формате: DATA[7:0] = {ECC[3:0], CFGx[3:0]}. В таблице 2 приведены конфигурационные данные DATA[7:0] с ECC[3:0] в зависимости от значения CFGx[3:0].

Таблица 2 - Конфигурационные данные DATA[7:0]

|

DATA[7:0] |

ECC[3:0] |

CFGx[3:0] |

|

0x00 |

0000 |

0000 |

|

0x71 |

0111 |

0001 |

|

0xB2 |

1011 |

0010 |

|

0xC3 |

1100 |

0011 |

|

0xD4 |

1101 |

0100 |

|

0xA5 |

1010 |

0101 |

|

0x66 |

0110 |

0110 |

|

0x17 |

0001 |

0111 |

|

0xE8 |

1110 |

1000 |

|

0x99 |

1001 |

1001 |

|

0x5A |

0101 |

1010 |

|

0x2B |

0010 |

1011 |

|

0x3C |

0011 |

1100 |

|

0x4D |

0100 |

1101 |

|

0x8E |

1000 |

1110 |

|

0xFF |

1111 |

1111 |

3.3.1 Среда разработки Keil

Для расположения конфигурационных значений CFGx по требуемым адресам в среде Keil может использоваться атрибут переменной __attribute__((section(".ARM.__at_ADDR"))). В фрагменте кода 1 приведены примеры объявления конфигурационных констант.

Фрагмент кода 1 - Объявления конфигурационных констант в среде Keil

/************************************************************/

#define __ATTR_ADDR(ADDR) __attribute__((section(".ARM.__at_"#ADDR)))

/* 8-ми разрядная шина данных, последовательная организация ECC */

const uint8_t Cfg_0 __ATTR_ADDR(0x10000400) = 0x71; //1 - 8-ми разрядная шина данных

const uint8_t Cfg_1 __ATTR_ADDR(0x10000408) = 0xB2; //2 - последовательная организация ECC

/* Базовый адрес ECC 0x1006_0000 */

const uint8_t Cfg_2 __ATTR_ADDR(0x10000410) = 0x00;

const uint8_t Cfg_3 __ATTR_ADDR(0x10000418) = 0x00;

const uint8_t Cfg_4 __ATTR_ADDR(0x10000420) = 0x00;

const uint8_t Cfg_5 __ATTR_ADDR(0x10000428) = 0x00;

const uint8_t Cfg_6 __ATTR_ADDR(0x10000430) = 0x66;

const uint8_t Cfg_7 __ATTR_ADDR(0x10000438) = 0x00;

const uint8_t Cfg_8 __ATTR_ADDR(0x10000440) = 0x00;

const uint8_t Cfg_9 __ATTR_ADDR(0x10000448) = 0x71;

/************************************************************/

/* 32-х разрядная шина данных, параллельная организация ECC */

const uint8_t Cfg_0 __ATTR_ADDR(0x10000400) = 0xC3; //3 - 32-х разрядная шина данных

const uint8_t Cfg_1 __ATTR_ADDR(0x10000408) = 0xC3; //3 - параллельная организация ECC

/************************************************************/

/* 16-ти разрядная шина данных, без проверки ECC */

const uint8_t Cfg_0 __ATTR_ADDR(0x10000400) = 0xB2; //2 - 16-ти разрядная шина данных

const uint8_t Cfg_1 __ATTR_ADDR(0x10000408) = 0x71; //1 - без ECC

3.3.2 Среда разработки IAR

Для расположения конфигурационных значений CFGx по требуемым адресам в среде IAR может использоваться оператор @ совместно с ключевым словом __root. В фрагменте кода 2 приведены примеры объявления конфигурационных констант.

Фрагмент кода 2 - Объявление конфигурационных констант в среде IAR

/************************************************************/

/* 8-ми разрядная шина данных, последовательная организация ECC */

_root const uint8_t Cfg_0 @ 0x10000400 = 0x71; //1 - 8-ми разрядная шина данных

_root const uint8_t Cfg_1 @ 0x10000408 = 0xB2; //2 - последовательная организация ECC

/* Базовый адрес ECC 0x1006_0000 */

_root const uint8_t Cfg_2 @ 0x10000410 = 0x00;

_root const uint8_t Cfg_3 @ 0x10000418 = 0x00;

_root const uint8_t Cfg_4 @ 0x10000420 = 0x00;

_root const uint8_t Cfg_5 @ 0x10000428 = 0x00;

_root const uint8_t Cfg_6 @ 0x10000430 = 0x66;

_root const uint8_t Cfg_7 @ 0x10000438 = 0x00;

_root const uint8_t Cfg_8 @ 0x10000440 = 0x00;

_root const uint8_t Cfg_9 @ 0x10000448 = 0x71;

/************************************************************/

/* 32-х разрядная шина данных, параллельная организация ECC */

_root const uint8_t Cfg_0 @ 0x10000400 = 0xC3; //3 - 32-х разрядная шина данных

_root const uint8_t Cfg_1 @ 0x10000408 = 0xC3; //3 - параллельная организация ECC

/************************************************************/

/* 16-ти разрядная шина данных, без проверки ECC */

_root const uint8_t Cfg_0 @ 0x10000400 = 0xB2; //2 - 16-ти разрядная шина данных

_root const uint8_t Cfg_1 @ 0x10000408 = 0x71; //1 - без ECC

4. Изменение параметров работы внешней шины

В ходе работы загрузочной программы в контроллере внешней шины устанавливаются следующие временные параметры транзакции на шине: WS_HOLD[3:0] = 0x4, WS_SETUP[3:0] = 0x4, WS_ACTIVE[7:0] = 0x7F. При необходимости в пользовательской программе данные параметры могут быть изменены. Для этого требуется разместить код функции, осуществляющей настройку контроллера внешней шины, во внутреннем ОЗУ, чтобы на момент внесения изменений исполнение программы происходило не из внешней памяти. Пример такой функции приведён во фрагменте кода 3.

Фрагмент кода 3 - Функция настройки временных параметров контроллера внешней шины

void EBC_RGNx_WSConfig(uint32_t RGNx, uint32_t RGN_WS_SETUP, uint32_t RGN_WS_ACTIVE, uint32_t RGN_WS_HOLD)

{

uint32_t tmpreg_CNTRL, *EBC_RGNx_CNTRL_ptr;

/* Check the parameters */

assert_param(IS_EBC_RGNx(RGNx));

assert_param(IS_EBC_RGNx_WS_SETUP(RGN_WS_SETUP));

assert_param(IS_EBC_RGNx_WS_ACTIVE(RGN_WS_ACTIVE));

assert_param(IS_EBC_RGNx_WS_HOLD(RGN_WS_HOLD));

EBC_RGNx_CNTRL_ptr = (uint32_t *)(&EXT_BUS_CNTR->RGN0_CNTRL) + RGNx;

/* Clear WS bits */

tmpreg_CNTRL = *EBC_RGNx_CNTRL_ptr & (~(EBC_WS_SETUP_MSK | EBC_WS_ACTIVE_MSK | EBC_WS_HOLD_MSK));

/* Form new value */

tmpreg_CNTRL |= RGN_WS_SETUP<<EBC_WS_SETUP_pos | RGN_WS_ACTIVE<<EBC_WS_ACTIVE_pos | RGN_WS_HOLD<<EBC_WS_HOLD_pos;

/* Configure CNTRL register with new value */

*EBC_RGNx_CNTRL_ptr = tmpreg_CNTRL;

/* Data Synchronization Barrier */

__DSB();

}

4.1 Среда разработки Keil

В среде Keil для расположения функции в памяти ОЗУ может использоваться атрибут __attribute__((section(«…»))), который задаётся при объявлении функции. В фрагменте кода 4 приведён пример объявления функции EBC_RGNx_WSConfig() с атрибутом «section» для размещения функции в секции «EXECUTABLE_MEMORY_SECTION».

Фрагмент кода 4 - Объявление функции с атрибутом «section»

void EBC_RGNx_WSConfig(uint32_t RGNx, uint32_t RGN_WS_SETUP, uint32_t RGN_WS_ACTIVE, uint32_t RGN_WS_HOLD) __attribute__((section("EXECUTABLE_MEMORY_SECTION")));

Чтобы секция «EXECUTABLE_MEMORY_SECTION» размещалась в памяти ОЗУ, необходимо отредактировать scatter-файл (конфигурационный файл компоновщика). В scatter-файлы необходимо указать, что секция «EXECUTABLE_MEMORY_SECTION» должна размещаться в ОЗУ, область RW_IRAM1, как показано во фрагменте кода 5.

Фрагмент кода 5 - Scatter-файл. Размещение секции «EXECUTABLE_MEMORY_SECTION» в RW_IRAM1

; *************************************************************

; *** Scatter-Loading Description File generated by uVision ***

; *************************************************************

LR_IROM1 0x20000000 0x00001000 { ; load region size_region

ER_IROM1 0x20000000 0x00001000 { ; load address = execution address

*.o (RESET, +First)

*(InRoot$$Sections)

.ANY (+RO)

}

RW_IRAM1 0x20001000 0x00001000 { ; RW data

*.o (EXECUTABLE_MEMORY_SECTION)

.ANY (+RW +ZI)

}

}

Подробное описание по размещению функций в ОЗУ в среде Keil приведено в статье «[i] Расположение функций в ОЗУ в IDE Keil».

4.2 Среда разработки IAR

В среде IAR для расположения функции в памяти ОЗУ может использоваться ключевое слово __ramfunc, которое задаётся при объявлении функции. В фрагменте кода 6 приведён пример объявления функции EBC_RGNx_WSConfig() с ключевым словом __ramfunc.

Фрагмент кода 6 - Объявление функции с ключевым словом __ramfunc

__ramfunc void EBC_RGNx_WSConfig(uint32_t RGNx, uint32_t RGN_WS_SETUP, uint32_t RGN_WS_ACTIVE, uint32_t RGN_WS_HOLD);

5. Подключение внешней памяти к МК

В данном пункте приведены примеры подключения внешней памяти к МК К1986ВЕ8Т для старта в режимах работы EXTBUS_8_ECC и EXTBUS_CFG. В качестве внешней памяти выбрана микросхема К1645РТ3У, которая имеет перенастраиваемую организацию, определяемую по состоянию на выводе CONF:- CONF = 0: 128К слов по 16 бит;

- CONF = 1: 256К слов по 8 бит.

При работе в 16-ти разрядном режиме (CONF = 0) сигнал адреса А17 игнорируется, вход А17 должен быть подключен к шине «Общий» или к шине «Питание».

5.1 Режим работы EXTBUS_8_ECC+JA(JB)

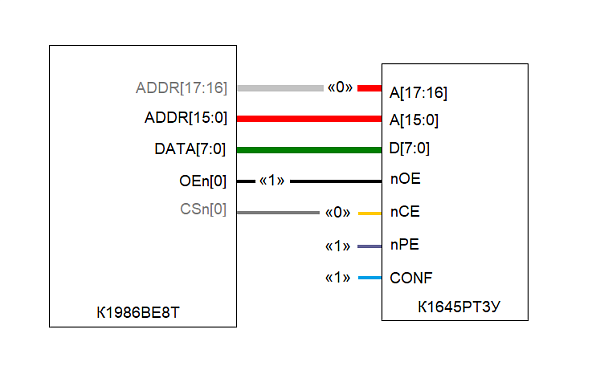

На рисунке 1 приведена структурная схема подключения микросхемы К1645РТ3У к МК К1986ВЕ8Т для старта в режиме работы EXTBUS_8_ECC. Микросхема К1645РТ3У работает в 8-ми разрядном режиме (CONF = 1). Объем пользовательской программы составляет до 36 Кбайт, ECC занимает до 12 Кбайт, остальная память регионом 0 не используется. Для МК К1986ВЕ8Т серым цветом показаны сигналы адреса и управления, которые не инициализируются загрузочной программой, но при необходимости могут быть настроены в пользовательской программе. Символы «0» и «1» обозначают подтяжку указанных выводов с помощью резисторов доопределения к шине «Общий» и шине «Питания» соответственно. Сигнал OEn[0] также доопределен до уровня логической «1» во избежание наводок во время запуска МК, когда вывод МК OEn[0] не сконфигурирован и находится в высокоимпедансном состоянии.Рисунок 1 - Структурная схема подключения микросхемы К1645РТ3У к МК К1986ВЕ8Т для старта в режиме EXTBUS_8_ECC

5.2 Режим работы EXTBUS_CFG+JA(JB)

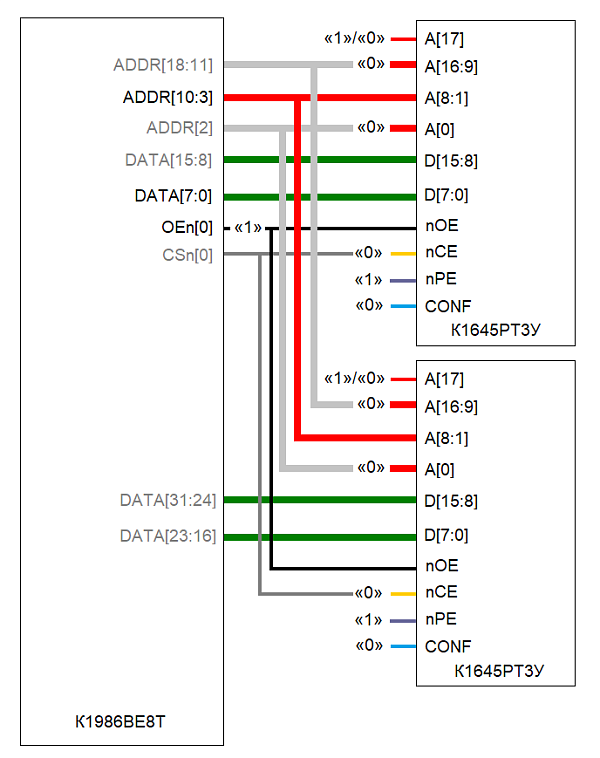

На рисунке 2 приведена структурная схема подключения двух микросхем К1645РТ3У к МК К1986ВЕ8Т для старта в режиме работы EXTBUS_CFG с использованием 32-x битной шины данных. Режим ECC может быть задан как с последовательной организацией ECC, так и без проверки ECC. Объем пользовательской программы составляет до 384 Кбайт с последовательной ECC и до 512 Кбайт без ECC.Микросхема К1645РТ3У работает в 16-ти разрядном режиме (CONF = 0). Для МК К1986ВЕ8Т серым цветом показаны сигналы адреса и управления, которые не конфигурируются загрузочной программой при первоначальной инициализации. В итоговой инициализации будет настроена шина адреса A[20:0], шина данных - в зависимости от CFG0, вывод CSn[0] при необходимости может быть настроен в пользовательской программе. Символы «0» и «1» обозначают подтяжку указанных выводов с помощью резисторов доопределения к шине «Общий» и шине «Питания» соответственно. Сигнал OEn[0] также доопределен до уровня логической «1» во избежание наводок во время запуска МК, когда вывод МК OEn[0] не сконфигурирован и находится в высокоимпедансном состоянии.

Рисунок 2 - Структурная схема подключения микросхемы К1645РТ3У к МК К1986ВЕ8Т для старта в режиме EXTBUS_CFG: 32-разрядная шина данных без параллельного ECC

Так как в МК К1986ВЕ8Т реализована байтовая адресация всех областей памяти, а адресация внешней шины зависит от разрядности шины данных, то для согласования адресации необходимо подключать шину адреса МК к микросхемам памяти со смещением. Величина смещения адресной шины МК в зависимости от адресации внешней шины приведена в таблице 3. Величина смещения показывает количество младших сигналов шины адреса МК, которые не подключаются к микросхеме памяти.

Таблица 3 - Величина смещения адресной шины МК в зависимости от адресации внешней шины

|

Смещение адресной шины МК, количество разрядов |

Адресация внешней шины (разрядность шины данных) |

|

Нет смещения |

8-ми битная |

|

1 |

16-ти битная |

|

2 |

32-х битная |

|

3 |

64-х битная |

Сохранить статью в PDF