Центра проектирования интегральных микросхем

|

Информационный портал технической поддержки Центра проектирования интегральных микросхем |

В микроконтроллерах, на базе ядер Cortex за работу с прерываний отвечает NVIC - Nested vector interrupt control, он же контроллер приоритетных векторных прерываний. NVIC является неотъемлемой частью процессоров M-профиля архитектуры ARM. В DSP процессорах его нет. В случае с серией К1967ВНxx, то в них за прерывания отвечает собственный контроллер, функционал которого похож на NVIC. В данном материалы попробуем поподробней разобраться в системе прерываний процессоров серии К1967ВНxx.

Документация на процессоры классифицирует прерывания следующим образом: аппаратные и программные. Далее по тексту программные прерывания называются программными исключения. Но к ним вернёмся чуть позднее. Общая схема процесса обработки прерывания представлена на рисунке 1 - она не сильно отличается от того, что мы привыкли видеть в ARM архитектуре при взаимодействии с NVIC.

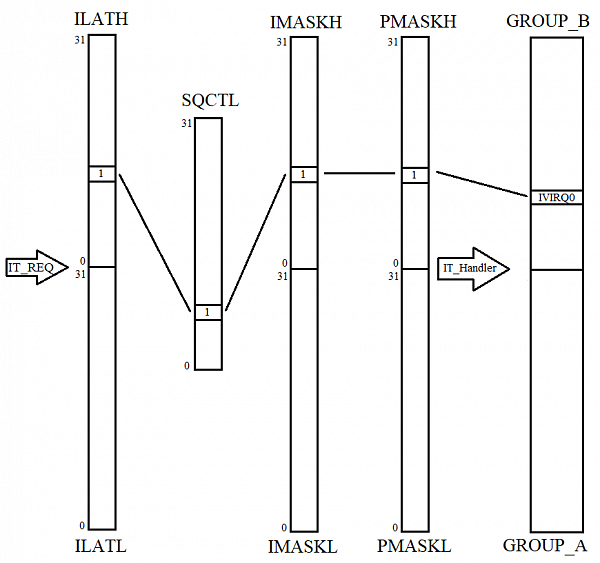

Рисунок 1 - Схема системы прерываний

Есть источники событий, как видно из рисунка они представлены в порядке убывания приоритета. Самое высокоприоритетное прерывание SW, и как отмечалось ранее оно же называется программным исключением. В название это заложено потому, что оно вызывается исполняемым кодом. То есть, вызывается при определенной ситуации выполнении команд. Например, доступ к длинным словам по не выровненному адресу. Также, данное прерывание может быть вызвано с помощью специальных команд TRAP, EMUTRAP. Стоит учитывать, что обработка данного прерывания отличия от обработки аппаратного. Далее по списку, начиная с HWERR, все этих события являются уже источниками аппаратных прерываний. Само прерывание HWERR говорит об аппаратной ошибке и может быть вызвано в случаях, когда, например, происходит доступ к отключенной SDRAM, ошибочная ситуация в DMA/AutoDMA, произошло широковещательное из внешней памяти и другие. Далее следуют высокоприоритетные прерывания от таймеров TIMER0/1H. Поскольку все приоритеты прерываний жестко заданы (в отличии от того же NVIC, где приоритет можно задать самому) для небольшой гибкости также добавили и прерывания от таймеров с низким приоритетом TIMER0/1L. nBUSLOCK - прерывание захвата шины происходит, когда процессор становится мастером шины. За ним, приоритетом ниже, следует векторное прерывание общего назначения VIRPT для использования другим мастером. nIRQ – прерывания от внешних источников (внешние прерывания). Далее следуют DMA13-0, то есть отдельное прерывание для каждого канала DMA, и прерывания для каждого из портов связи - LINK3-0. И остался последний источник прерываний KERNEL – являющий прерыванием от ядра.

Теперь вернувшись к рисунку 1, видно, что после источников событий и самого контроллера прерываний, следуют группы регистров прерываний. Именно в эти регистры задается адрес функции обработчика прерываний. То есть, если NVIC он всегда фиксирован, то здесь он задается с помощью данных регистров.

Рассмотрим регистры блока прерываний и проведем аналогию всё с тем же NVIC из серии Cortex-M.

При работе с прерываниями основными в NVIC являются:

ISPR – регистр признака отложенного прерывания;

ISER – регистр разрешения прерываний;

IABR – регистр активных прерываний.

В процессорах ЦОС в аналогичных ролях выступают следующие регистры описания у них немного отличается, но суть функционала такая же:

ILAT – регистр «защёлки» прерываний;

IMASK – регистр маски или разрешения прерывания;

PMASK – регистр запросов прерываний, которые поступают на приоритетный шифратор.

Указанные выше регистры по документации являются 64 – разрядными, которые доступны как 2 32-разрядных регистра ILATL/ILATH, IMASKL/IMASKH, PMASKL/PMASKH. Регистр «защелки» имеет также два дублирующих регистра: для установки и сброса разрядов.

Помимо перечисленных в контроллере прерываний также присутствуют регистры для внутреннего таймера, а также регистр INRCTL который позволяет дать источникам прерываний небольшую «гибкость» при формировании запросов. К примеру, с его помощью можно настроить условие возникновение запроса внешнего прерывания.

И конечно, большим отличием от серии Cortex являются ранее упомянутые регистры группы прерываний А и B в которые заносятся адреса функции обработки прерываний. Куда для каждого прерывания задается адрес функции обработчика.

Рисунок 2 - Схема работы внешнего прерывания

На рисунке 2, на примере прерывания от внешнего вывода nIRQ0, рассмотрена схема работы системы прерываний.

Как только приходит запрос на прерывание от устройства, он «защелкивается» и в регистре ILAT, соответствующему прерыванию выставляется бит запроса. Затем проверяется его маска, разрешен ли данный запрос в регистре IMASK. Здесь стоит отметить, что также должен быть выставлен бит глобального разрешения прерываний GIE, в регистре управления SQCTL. Если все эти условия выполнены и прерыванием является самым высокоприоритетным на данный момент, то ядро переходит по адресу обработчика прерываний и приступает к его обработке.

К данной статье приложен пример для отладочной платы микросхемы К1967ВН02BG, в котором демонстрируется работа внешнего прерывания по схеме, приведённой выше. В программе процессор постоянно моргает двумя верхними диодами на плате, а при нажатии и удерживании кнопки DSP1_IRQ0 на отладочной плате, происходит прерывание и моргает уже нижняя пара светодиодов.

Вся настройка данного прерывания очень простоя и приведена ниже:

__builtin_sysreg_write(__IVIRQ0, (int) INT); // Установить адрес функции прерывания

__builtin_sysreg_write(__SQCTLST, 4); // Включить глобальные прерывания

__builtin_sysreg_write(__IMASKH, 1 << 9); // Разрешить прерывание по внешнему выводу IRQ0

Единственное, надо не забыть указать компилятору с помощью специального атрибута, какая функция является обработчиком прерывания:

__attribute((interrupt))

void INT(void)

{

.........

}

| Сайт: | https://support.milandr.ru |

| E-mail: | support@milandr.ru |

| Телефон: | +7 495 221-13-55 |