Центра проектирования интегральных микросхем

|

Информационный портал технической поддержки Центра проектирования интегральных микросхем |

При включении питания микросхемы запускаются на частоте HSI-генератора.

Для корректной смены тактовой частоты ядра сначала должны быть сформированы необходимые тактовые частоты, и затем осуществлено переключение на них на соответствующих мультиплексорах, управляемых регистрами CPU_CLOCK.

Для переключения с одного источника частоты на другой нужно, чтобы оба источника оставались включенными.

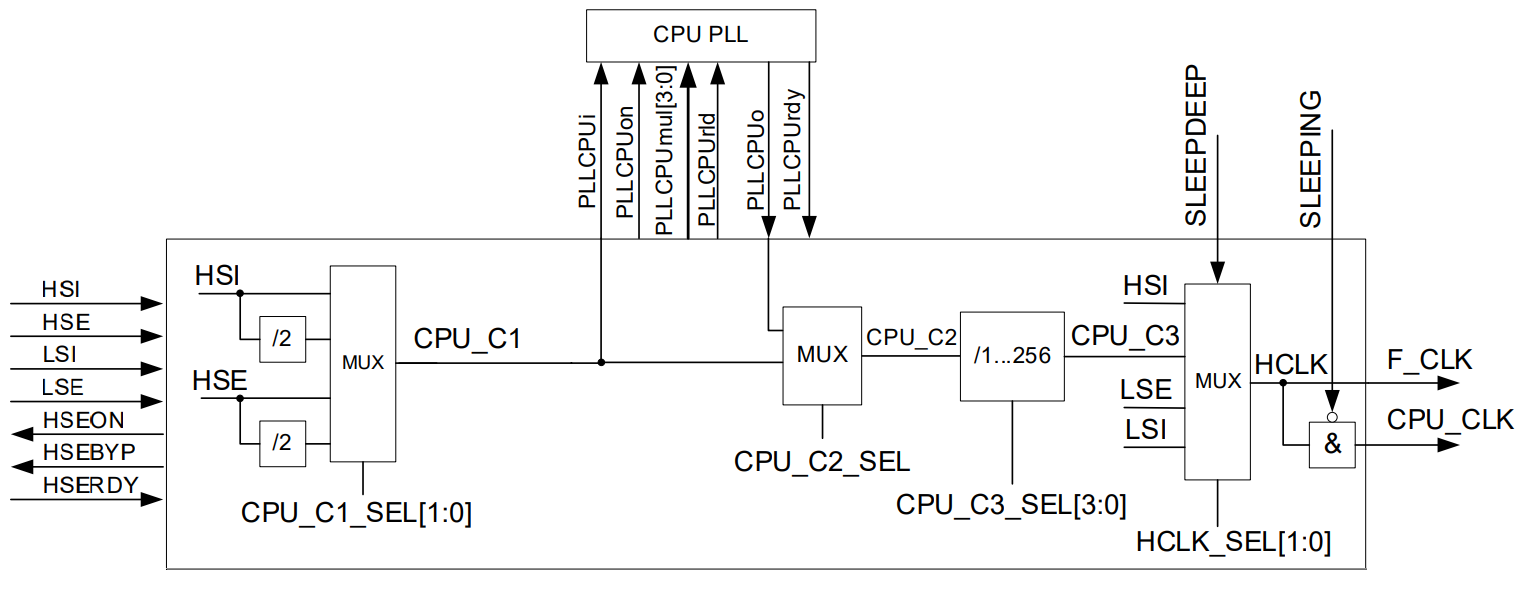

Рисунок 1 - Тракт тактовой частоты ядра

Для инициализации тактовой частоты HCLK (см. рис. 1) необходимо:

1) настроить (разрешить работу и дождаться выхода в рабочий режим) источник частоты для CPU_C1, если он не был настроен (см. п. 15.1 "Встроенный RC-генератор HSI", п. 15.3 "Внешний генератор HSE").

2) Выбрать источник для CPU_C1 (поле CPU_C1_SEL регистра MDR_RST_CLK->CPU_CLOCK).

3) Если в качестве источника для CPU_C2 выбирается CPU_PLL – настроить CPU_PLL, включить и дождаться установки нормального режима работы.

4) Выбрать источник для CPU_C2 (поле CPU_C2_SEL регистра MDR_RST_CLK->CPU_CLOCK).

5) При необходимости установить делитель для CPU_C3 (поле CPU_C3_SEL регистра MDR_RST_CLK->CPU_CLOCK).

6) Если настраиваемая частота HCLK выше текущей частоты HCLK, то до выбора источника для HCLK необходимо:

- настроить число тактов паузы для доступа к Flash-памяти в соответствии с настраиваемой частотой (задается в регистре MDR_EEPROM->EEPROM_CMD битами Delay);

- выбрать режим работы встроенного регулятора напряжения DUCC (поле LOW регистра MDR_BKP->REG_0E) и выбрать дополнительную стабилизирующую нагрузку для встроенного регулятора напряжения DUCC (поле SelectRI регистра MDR_BKP->REG_0E) под настраиваемую частоту.

7) Выбрать источник для HCLK (поле HCLK_SEL[1:0] регистра MDR_RST_CLK->CPU_CLOCK).

8) Если выбранная частота для HCLK ниже предыдущей частоты HCLK, то после выбора источника для HCLK нужно:

- настроить число тактов паузы для доступа к Flash-памяти в соответствии с настроенной частотой (задается в регистре MDR_EEPROM->EEPROM_CMD битами Delay);

- выбрать режим работы встроенного регулятора напряжения DUCC (поле LOW регистра MDR_BKP->REG_0E) и выбрать дополнительную стабилизирующую нагрузку для встроенного регулятора напряжения DUCC (поле SelectRI регистра MDR_BKP->REG_0E) под настроенную частоту.

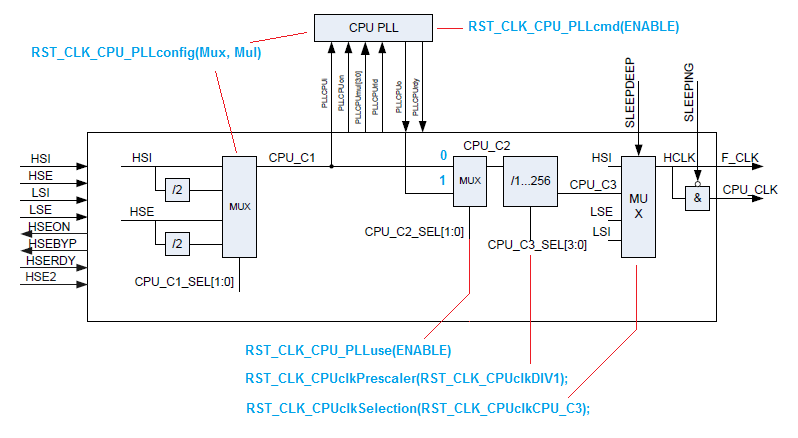

На рисунке 2 показано, как функции SPL влияют на выбор частоты тактирования ядра в микроконтроллере К1986ВЕ1QI. Для микроконтроллера К1986ВЕ92QI схема аналогичная.

Рисунок 2 - Тактирование ядра К1986ВЕ1QI

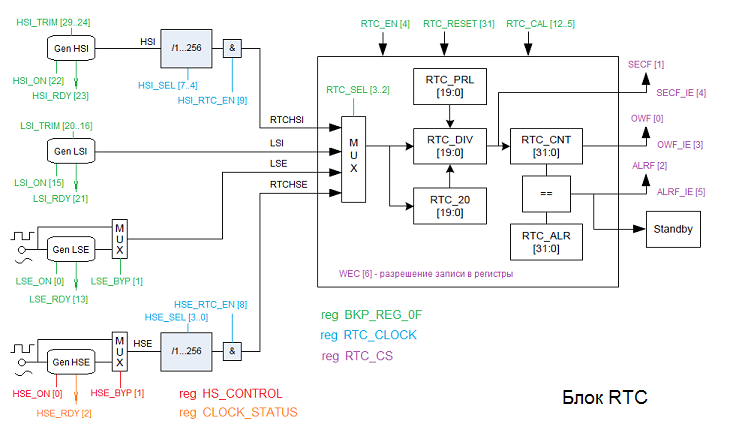

Рисунок 3 - Тактирование блока RTC

| Сайт: | https://support.milandr.ru |

| E-mail: | support@milandr.ru |

| Телефон: | +7 495 221-13-55 |