Центра проектирования интегральных микросхем

|

Информационный портал технической поддержки Центра проектирования интегральных микросхем |

В данной статье рассматривается общая информация по блоку таймеров общего назначения, которая поможет освоить соответствующий раздел спецификации. Необходимо отметить, что таймеры в различных микроконтроллерах несколько различаются.

В каждом микроконтроллере присутствует несколько таймеров общего назначения. Например, в МК семейства К1986ВЕ9x реализовано три 16-разрядных таймера, а в МК семейства К1986ВЕ1x - четыре 32-разрядных таймера. Каждый таймер обеспечивает свой счет и генерацию прерываний согласно настройкам.

В каждом таймере существует по четыре канала, каждый из которых может независимо работать как в режиме ШИМ (генерация импульсов), так и в режиме захвата. Для реализации этих режимов используются выводы GPIO, настроенные как выход для ШИМ и как вход для захвата внешнего сигнала.

В режиме ШИМ используется от одного до двух выводов GPIO, настроенных как выход. На один вывод, называемый "прямым", подается генерируемый таймером сигнал заданной скважности. На второй вывод, называемый "инверсным", выводится сигнал, инверсный относительно прямого вывода. Инверсный вывод используется не всегда, в основном он необходим для моторов, требующих такого управления. При использовании обоих выводов иногда требуется разнести во времени фронты переключения прямого и инверсного сигналов, чтобы исключить протекание сквозного тока в момент общего переключения. Для этого используется контроллер "мертвой зоны", который задает необходимую задержку между фронтами. Когда инверсный вывод не используется, то вывод GPIO для него можно не занимать.

При управлении моторами также бывает необходима функция аварийной остановки, когда таймер перестает выводить ШИМ, переключение выводов прекращается. Для этого в таймере есть внешние входы BRK и ETR, они так же должны быть назначены на GPIO в случае надобности. BRK - это аварийный вход, а ETR (External Timer Reference) помимо аварийного использования служит для задания внешней частоты счета. Подробнее про частоту счета в 2. Режим счетчика. Необходимо отметить, что BRK останавливает ШИМ асинхронно, а ETR - синхронно с частотой тактирования таймера.

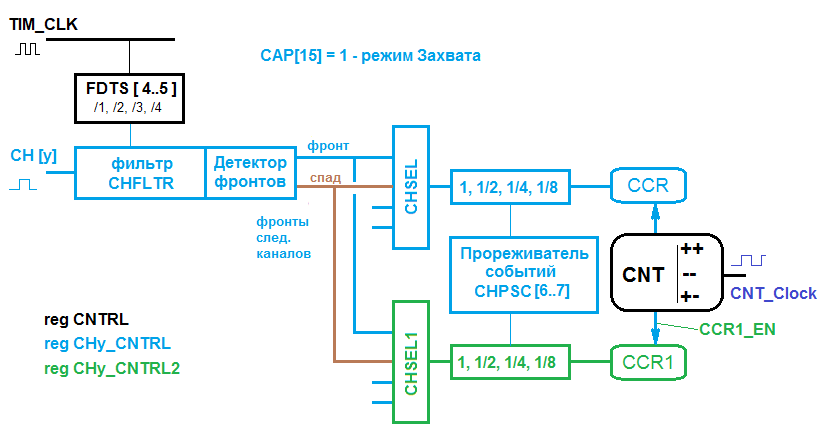

В режиме захвата используется только один внешний вывод - прямой, настраивается он как вход. В этом режиме счетчик записывает в регистрах CCR и CCR1 значение регистра CNT в момент обнаружения на входе фронта или спада внешнего сигнала.

Необходимо отметить, что каждый таймер работает на своей тактовой частоте TIM_CLK, которая формируется из контроллера тактовых частот. Вся работа таймера, захват и ШИМ режимы выполняются по переднему фронту сигнала TIM_CLK. Таким образом, при задании TIM_CLK равной частоте ядра достигается максимальная точность захвата фронта внешнего сигнала. То есть если внешний сигнал поменяет уровень между фронтами TIM_CLK, то захват этого события случится на ближайшем фронте TIM_CLK, а не где-то посередине.

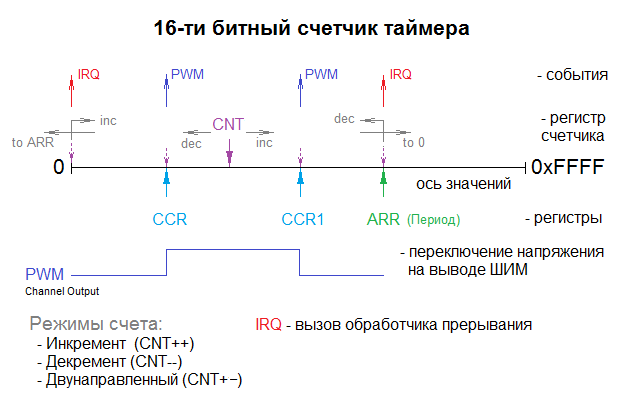

Основная задача счетчика - это считать число входных импульсов. Количество импульсов считается в регистре CNT. Для того чтобы ограничить верхнюю границу счета используется регистр ARR (Auto-Reload Register). При достижении регистром CNT значения, заданного пользователем в ARR, генерируется прерывание, и счет начинается заново. Таким образом, регистр ARR является своего рода периодом, поскольку его можно использовать для генерации прерываний с заданным периодом времени.

Рисунок 1 - 16-разрядный счетчик таймера

Счет в регистре CNT может происходить не только в сторону увеличения. Доступны режимы:

Прерывания могут генерироваться, когда (CNT == ARR) и когда (CNT == 0), это задается флагами в регистре IE. Событие совпадения CNT с регистрами CCR и CCR1 используется в режиме ШИМ и описано в соответствующем разделе ниже.

Совпадения CNT с 0 и ARR, могут являться "событиями счета" для других таймеров, подключенных каскадно. Например, TIMER1 может отсчитывать 16 младших бит от общего количества входных импульсов, а TIMER2 старшие 16 бит. При этом каждое событие CNT==ARR в TIMER1, увеличивает на 1 регистр CNT в TIMER2. Таким образом, реализуется составной 32-битный таймер на основе двух 16-разрядных.

Двунаправленный режим счета обычно используется для того, чтобы прерывания возникали в центре импульсов, генерируемых таймером в режиме ШИМ. Подробнее об этом далее.

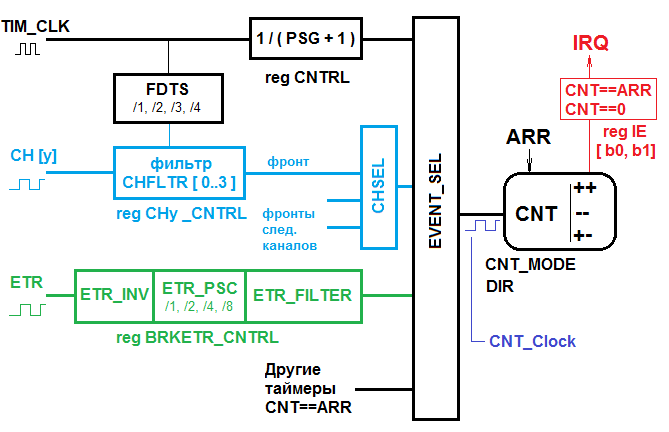

Источников входных импульсов ("событий счета") может быть несколько, все они приведены на рисунке 2.

Рисунок 2 - Источники "событий счета"

Передний фронт сигнала будем называть просто "фронт", а задний фронт называть "спад". Регистры и относящиеся к ним биты помечены одинаковыми цветами.

"Событием счета" - может выступать:

Событие счета и направление счета задаются в регистре CNTRL в битовых полях, представленных в таблице 1.

Таблица 1 - Настройка события и направления счета в регистре CNTRL

| Событие счета | EVENT_SEL[3:0] | CNT_MODE[1:0] | DIR | Режим счета |

|---|---|---|---|---|

| Фронт TIM_CLK | b0000 | b00 | b0 | CNT++ |

| b1 | CNT-- | |||

| b01 | bx | CNT+- | ||

|

CNT==ARR в таймерах |

b000-b0011 b1010 |

b10 | b0 | CNT++ |

| b1 | CNT-- | |||

|

Фронт на входе канала таймера |

b01хх | b10 | b0 | CNT++ |

| b1 | CNT-- | |||

|

Фронт или спад на входе ETR |

b1000 b1010 |

b10 | b0 | CNT++ |

| b1 | CNT-- |

Символом "х" помечены биты, значения которых не учитываются в заданном режиме.

Как видно из таблицы, направление счета, как правило, задается битом DIR. Исключением является случай счета вперед-назад, который доступен только по фронту внутреннего тактирования TIM_CLK.

Регистр CNT изменяется на каждом фронте сигнала TIM_CLK, прошедшего через делитель, который определяется регистром PSG. То есть частота счета получается TIM_CLKd = TIM_CLK / ( PSG + 1).

Событие CNT==ARR в таймерах используется для объединения нескольких таймеров в общий таймер-счетчик с большей разрядностью.

Когда прямой GPIO-вывод канала настроен в режим захвата, то фронт сигнала на этом входе может служить источником событий для счета. Такой режим полезен для подсчета количества каких-то внешних событий. Важно отметить, что событием счета всегда является фронт внешнего сигнала вне зависимости от настройку поля CHSEL[1:0] в регистре CHy_CNTRL.

Внешний сигнал от данного входа дополнительно может быть отфильтрован, подробнее в 3. Фильтрация входного сигнала.

Каждый таймер имеет отдельный внешний вывод ETR, который всегда используется как вход. Фронт или спад (в зависимости от выставленного бита ETR_INV регистра BRKETR_CNTRL - по умолчанию ETR_INV = 0 (счёт CNT по фронту)) сигнала на данном выводе могут также быть источником изменения CNT. Вход ETR необходим, чтобы оставить каналам таймера их основную функциональность - работу в режимах ШИМ (Широтно-Импульсной Модуляции) и захвата, при этом счет будет происходить по сигналу с ETR.

Внешний сигнал от данного входа дополнительно может быть отфильтрован, подробнее в 3. Фильтрация входного сигнала.

Когда таймер считает импульсы с внешнего входа, может возникнуть необходимость отфильтровать помехи и исключить ложные срабатывания при колебаниях сигнала на входе. Для этого внешние сигналы проходят через фильтр, который пропускает только те сигналы, которые соответствуют ожидаемой длительности импульса.

Поскольку внешние импульсы могут быть заведены через входы каналов и вывод ETR, то у каждого из этих входов есть свои фильтры. Для канала таймера значение фильтра задается в регистре CHy_CNTRL битами CHFLTR[3:0]. А для ETR в регистре BRKETR_CNTRL битами ETR_FILTER[3:0]. Значение этих полей определяет длительность импульса на входе, чтобы считаться достоверным, а не помехой.

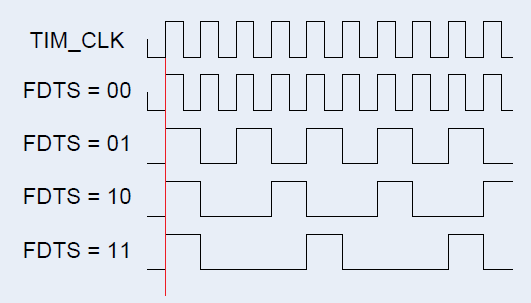

Поскольку частота TIM_CLK часто настраивается достаточно высокой для достижения наименьшей погрешности определения фронтов, то использовать ее для проверки длительности входного сигнала может быть неудобно. Потребуется счетчик большой разрядности, чтобы замерять в тактах TIM_CLK относительно длинные входные импульсы. Для упрощения счета ввели производную от TIM_CLK частоту - FDTS, которая наравне с TIM_CLK используется для задания фильтрации (рисунок 3).

Рисунок 3 - Частота FDTS

Частота FDTS в периодах TIM_CLK задается в регистре CNTRL в битах DTS[1:0]. Максимальное значение DTS[1:0] = 3 формирует частоту FDTS = TIM_CLK / 4. (В спецификации описанные биты называются FDTS[1:0]. В данной статье, чтобы не возникла путаница, частота называется FDTS, а управляющие биты - DTS.)

Рисунок 4 показывает счет события по переднему фронту входного сигнала с фильтрацией.

Рисунок 4 - Счет события по переднему фронту входного сигнала с фильтрацией

ВАЖНО! В данном случае на рисунке 4 представлен гипотетический вариант, когда фильтр состоит из 2-х триггерах с частотой FDTS / 2. Ближайшее реально возможное значение CHFLTR[3:0] = b0100 конфигурирует фильтр на 6 триггеров с частотой FDTS / 2, но этот вариант сложно отобразить на рисунке - он получится слишком длинным.

Рисунок 4 показывает, что:

В случае с использованием сигнала счета с ETR рисунок будет аналогичным, только конфигурация фильтра происходит в регистре BRKETR_CNTRL. Также для сигнала ETR есть дополнительный инвертор и предделитель внешней частоты. Предделитель используется тогда, когда используется внешний стабильный сигнал тактирования счета, и нет необходимости в фильтрации коротких импульсов.

Каждый канал таймера может работать в режиме захвата. В этом режиме канал "детектирует" фронты и спады сигнала на прямом канале таймера. Происходит это следующим образом:

Рисунок 5 - Работа таймера в режиме захвата

В регистре CHy_CNTRL в поле CHSEL[1:0] задается по какому событию CNT будет сохраняться в CCR, по фронту или по спаду. Аналогичный выбора события для CCR1 осуществляется в регистре CHy_CNTRL2 поле CHSEL1[1:0].

Делитель позволяет захватывать не каждое событие, а лишь каждое второе, четвертое или восьмое. Настройка делителя происходит в поле CHPSC[1:0] регистра CHy_CNTRL.

Таким образом, в двух регистрах CCR и CCR1 "захватывается" значение CNT в тот или иной момент. Настроив CCR на фронт, а CCR1 на спад, можно узнать длительность импульса в отсчетах времени регистра CNT. Отследив изменение CCR, несложно также получить и период сигнала.

Регистр CCR1 используется не всегда - он подключается опционально. Для использования CCR1 его необходимо включить в регистре CHy_CNTRL2 битом CCR1_EN.

При измерении сигнала для захвата могут быть использованы все настройки фильтрации, описанные выше в разделе 3. Фильтрация входного сигнала. То есть можно сделать так, чтобы фронты и спады захватывались только у импульсов определенной длительности.

Инверсный вывод GPIO канала таймера в данном режиме не используется. Прямой вывод должен быть настроен как вход, в регистре CHy_CNTRL1 поле SELOE[1:0] = 0. Подробнее в описании данного поля в разделе ШИМ.

Каждый канал таймера может работать в режиме ШИМ (широтно-импульсной модуляции), то есть генерировать импульсы заданной длины при заданном периоде. Для этого также используются регистры CCR и CCR1, которые разбивают диапазон значений CNT от 0 до ARR на необходимые интервалы. При совпадении значения CNT с одним из регистров CCR и CCR1 меняется уровень выходного сигнала REF. Как именно изменяется сигнал REF при совпадении регистров, настраивается в CHy_CNTRL полем OCCM[2:0].

Регистр CCR1 используется не всегда - он подключается опционально. Для использования CCR1 его необходимо включить в регистре CHy_CNTRL2 битом CCR1_EN.

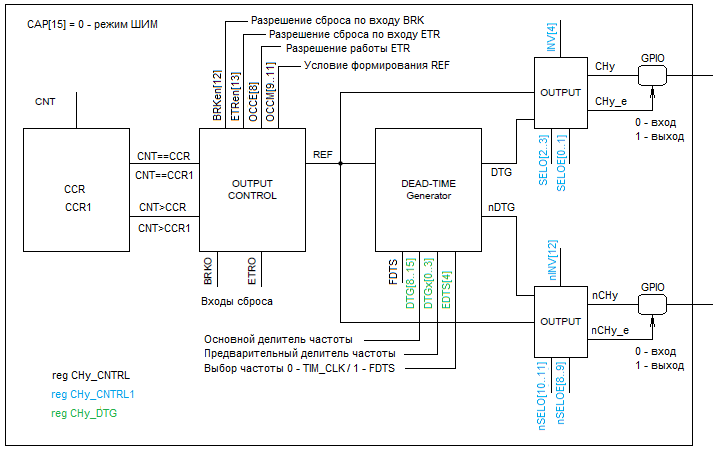

Рисунок 6 - Структурная схема блока формирования ШИМ

Сигнал REF - это внутренний сигнал, он может непосредственно подаваться на выводы канала таймера (прямой и инверсный), либо пропускаться сначала через блок DTG, а затем подаваться на выводы. При стандартных настройках на инверсный вывод автоматически подается сигнал, инвертированный относительно прямого вывода.

За подачу сигналов на прямой и инверсный выводы отвечает регистр CHy_CNTRL1, здесь для каждого из выводов своя настройка. Поле SELO[1:0] определяет, какой сигнал подается на выход.

Таблица 2 - Настройка выходного сигнала ШИМ

| SELO[1:0] | Выход GPIO |

|---|---|

| 00 | "0" |

| 01 | "1" |

| 10 | REF |

| 11 | DTG |

DTG - это сигнал REF, прошедший через блок DTG. Помимо сигналов ШИМ может выводиться постоянный уровень "0" или "1".

Бит INV позволяет инвертировать выходной сигнал.

При назначении вывода МК в функцию канала таймера, состояние ОЕ данного вывода необходимо задать в регистре SELOE[1:0]. То есть у каждого канала есть внутренний сигнал разрешения CHyoe (nCHyoe). Этот сигнал уходит в блок GPIO и задает, будет ли вывод канала являться входом или выходом. Если на CHyoe подана "1", то канал работает как выход и выводит сигнал, определенный полем SELO[1:0]. Если CHyoe = 0, то вывод является входом. В случае работы в режиме захвата с этого вывода захватывается сигнал.

Значение сигнала разрешения задается в поле SELOE[1:0]. Кроме ручного выставления "0" и "1", доступен вариант, когда для сигнала разрешения используется сигнал REF или DTG. В этом случае текущий уровень выбранного сигнала определяет, работает ли канал на выход или находится в Z состоянии.

Таблица 3 - Настройка входа/выхода канала таймера

| SELOE[1:0] | REF / DTG | Выход GPIO |

|---|---|---|

| 00 | - | Z |

| 01 | - | SELO[1:0] |

| 10 | REF: 0 / 1 | Z / SELO[1:0] |

| 11 | DTG: 0 / 1 | Z / SELO[1:0] |

Для инверсного вывода доступны такие же поля с префиксом N - NSELO[1:0], NINV, NSELOE[1:0].

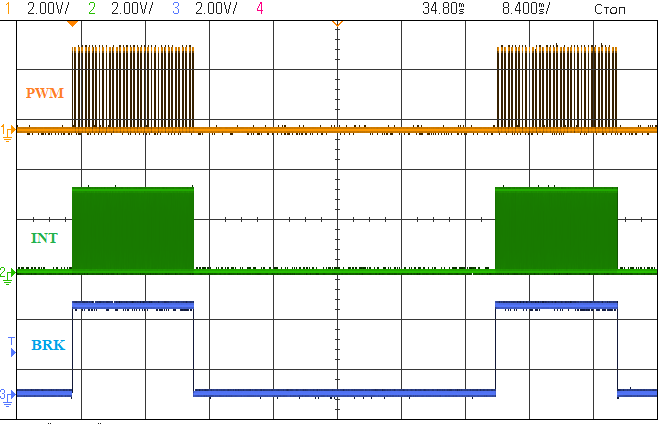

Назначение входов ETR и BRK было описано в начале статьи - они служат для аварийной остановки ШИМ. Рисунок 7 показывает активные уровни ETR и BRK, при которых сбрасывается сигнал ШИМ. Необходимо отметить, что по умолчанию эти уровни инверсны друг относительно друга. Инверсию можно настроить в регистре BRKETR_CNTRL. Работу вывода ETR необходимо разрешить битом CHy_CNTRL.OCCE=1, для BRK дополнительных настроек не требуется.

Рисунок 7 - Уровни сигналов ETR и BRK

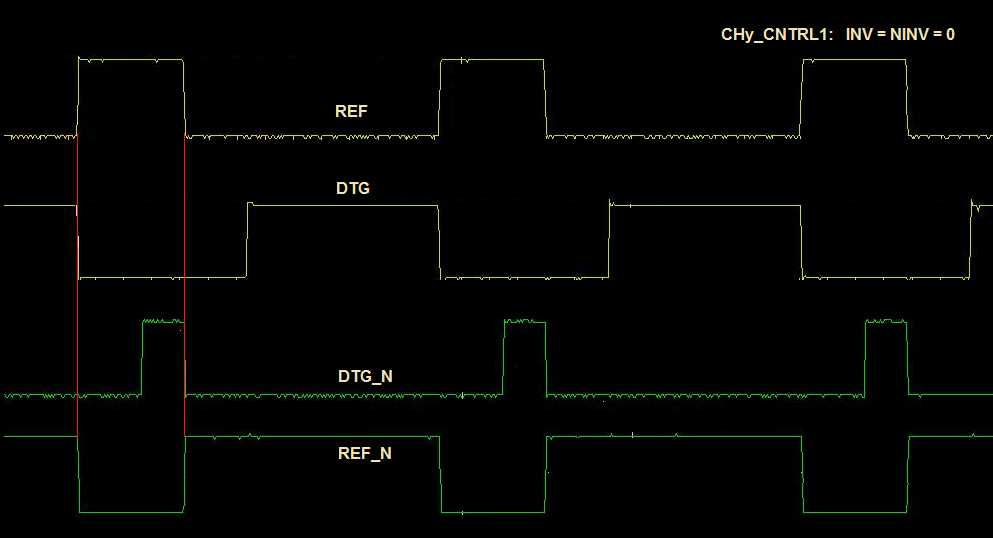

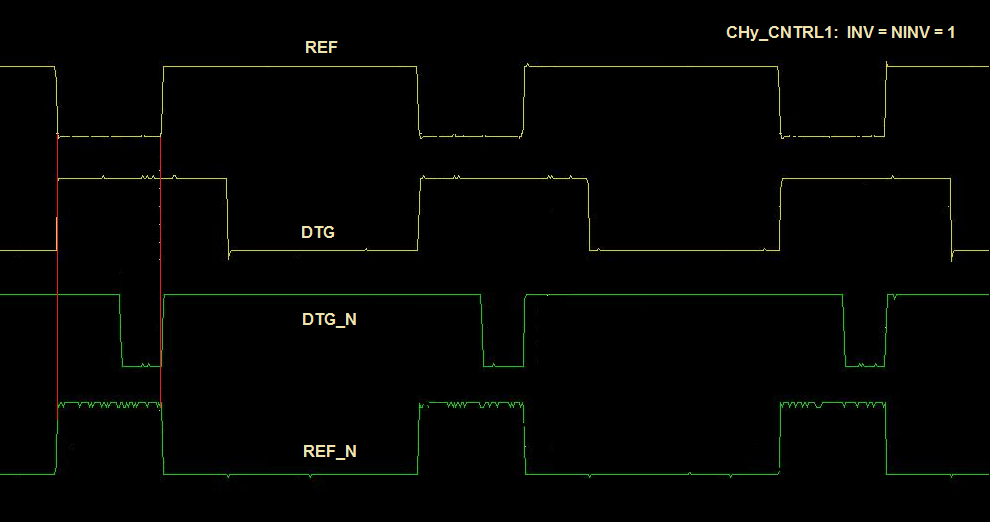

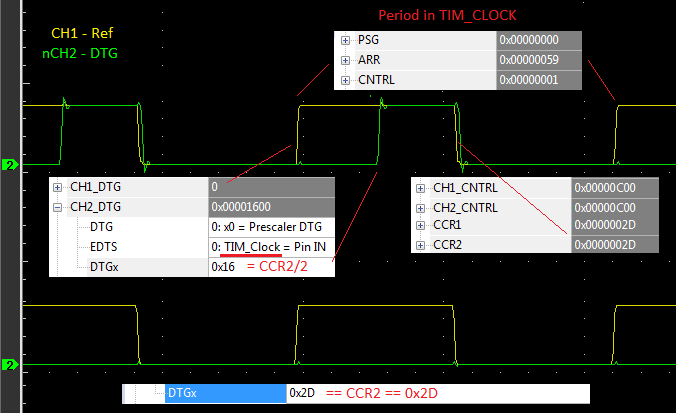

Как уже упоминалось в начале статьи, мертвая зона требуется для того, чтобы исключить протекание сквозного тока при одновременном переключении фронтов на прямом и инверсном выводах. Для того чтобы на выводы подавался не сигнал REF, а сигнал DTG, необходимо в регистре CHy_CNTRL1 задать поля SELO[1:0] = NSELO[1:0] = 3, при этом поля SELOE[1:0] = NSELOE[1:0] = 1.

Если смотреть осциллографом вывод канала таймера, то можно заметить, что при переключении с REF на DTG сигнал, наблюдаемый на осциллографе, инвертировался. То есть, например, если при выводе REF длительность логической "1" составляла 30%, то при выводе сигнала с DTG эти 30% занимает логический "0". Если при этом включить инвертирование в том же регистре CHy_CNTRL1 битами INV = NINV = 1, то сигнал на выходе вновь станет таким же, каким был только что при выводе REF. Но необходимо учитывать, что перекрытие фронтов теперь получается совершенно иное. По этой причине для управления скважностью необходимо перестроить регистр CCR, а не использовать инверсии. Нагляднее эта ситуация представлена на рисунках 8 - 11 (осциллограммы, полученные на К1986ВЕ9x).

Рисунок 8 - Сигналы REF и DTG на выводах микроконтроллера К1986ВЕ9x при скважности 30% (смещение DTG в данных графиках гипертрофировано для наглядности)

По рисунку 8 видно, что на выходе прямого и инверсного выхода каналов не случается ситуации, когда логическая "1" присутствует на обоих выводах.

Рисунок 9 - Сигналы REF и DTG на выводах микроконтроллера К1986ВЕ9x, включена инверсия выводов (происходит перекрытие зон логической "1")

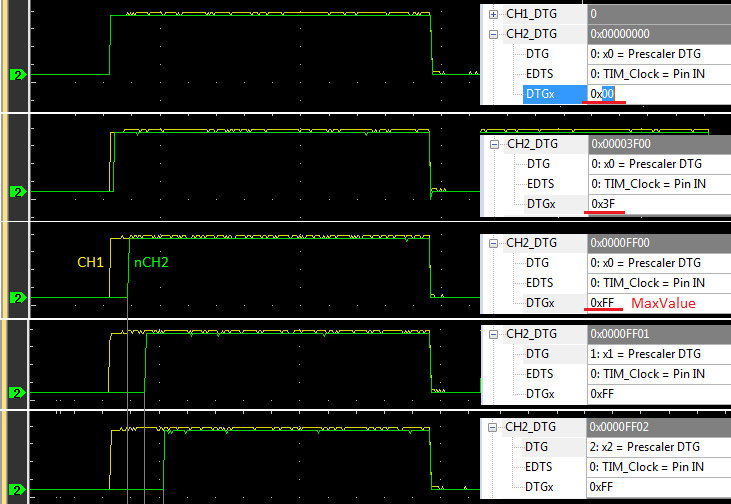

Для задания фазы сигнала DTG по сравнению с сигналом REF необходимо выбрать частоту, в периодах которой будет задаваться сдвиг. Эта частота задается полем CHy_DTG.EDTS - можно выбрать периоды частоты TIM_CLK или FDTS. Количество периодов задается полями регистра CHy_DTG.DTG[7:0], далее это количество умножается множителем в поле CHy_DTG.DTGx[3:0].

На рисунке 10 показан случай, когда в TIM_Clock задается и частота выходного сигнала задается, и сдвиг для DTG. Поэтому, если задать сдвиг, равный значению в регистре CCR2, то выходной сигнал пропадает. Это объясняется тем, что сдвиг становится равен длительности высокого уровня выходного сигнала. На рисунке 10: желтый сигнал - это сигнал REF с канала 1 таймера CH1, а зеленый сигнал - это сигнал DTG с выхода nCH2. Здесь учтено, что сигнал REF, проходя блок DTG, инвертируется. А поскольку удобнее сравнивать сигналы одной полярности, то выбрана именно эта пара (качество сигнала не являлось критичным, поэтому расхождение задних фронтов не стоит принимать во внимание).

Рисунок 10 - Сигналы REF и DTG в случае, когда частота выходного сигнала и сдвиг для DTG задаются в TIM_Clock

Рисунок 11 показывает, как влияют параметры CHy_DTG.DTG[7:0] и CHy_DTG.DTGx[3:0] на фазу сигнала DTG

Рисунок 11 - Влияние параметров CHy_DTG.DTG[7:0] и CHy_DTG.DTGx[3:0] на фазу сигнала DTG

В регистре CNTRL есть бит WR_CMPL, который при значении "0" разрешает запись в регистры CNT, ARR, PSG. Значение "1" означает, что идет запись. Аналогичные биты WR_CMPL и WR_CMPL1 есть в регистре CHy_CNTRL, которые отражают завершенность записи в регистры CCR и CCR1. Биты WR_CMPL не сбрасываются, если не подана частота TIM_CLK на блок таймера. Разрешение подачи частоты TIM_CLK выполняется в контроллере тактовых частот.

Для одновременного запуска нескольких таймеров необходимо сначала включить тактирование таймеров и инициализировать их без разрешения работы. Далее необходимо отключить частоту TIM_CLK, включить таймеры, а затем разрешить тактирование TIM_CLK одной записью в регистр контроллера тактовых частот. Важно отметить, что разрешение подачи тактирования в одном регистре реализовано не во всех МК, например, это не реализовано в К1986ВЕ8Т и К1986ВК01GI. Пример одновременного запуска таймеров 1 и 2 в МК К1986ВЕ9x приведен ниже.

// Тактирование для управления регистрами

MDR_RST_CLK->PER_CLOCK |= (3<<14); // Подача тактовой частоты для таймеров

MDR_RST_CLK->TIM_CLOCK = (3<<24);

// Настройки таймеров

TMR1_HW_Init();

TMR2_HW_Init();

// Отключение тактовой частоты для таймеров

MDR_RST_CLK->TIM_CLOCK = 0x0000;

// Запуск тактовой частоты на таймеры

MDR_TIMER1->CNTRL |= 0x0001;

MDR_TIMER2->CNTRL |= 0x0001;

// Подача частоты счета - синхронный запуск

MDR_RST_CLK->TIM_CLOCK = (3<<24);

Событие захвата происходит по фронту тактовой частоты таймера TIM_CLK. Если на некотором фронте сигнал на входе канала поменял значение, например, был логический "0", а стал "1", то генерируется сигнал возникновения события, который уходит в контроллер тактовых частот и DMA. На следующем такте TIM_CLK значение CNT сохраняется в регистры CCR и/или CCR1 и служит значением, при котором было зафиксировано событие.

Но частота TIM_CLK может быть много меньше, чем частота ядра. Если контроллер тактовых частот получит сигнал на прерывание от события, то ядру потребуется несколько тактов на то, чтобы войти в прерывание и начать исполнять код. Если этот код считывает значение CCR, то это значение может оказаться старым, еще не обновленным, потому что такт TIM_CLK еще не прошел.

Чтобы избежать подобного сценария, в регистры CHx_CTRL2 таймеров добавлен 4-й бит, который называется EV_DELAY. При выставлении этого бита в "1", выставление флагов и генерация сигналов событий происходит синхронно с обновлением регистров CCR. То есть, если стоит флаг события захвата, то можно считывать регистр CCR, значение в нем заведомо обновлено.

| Сайт: | https://support.milandr.ru |

| E-mail: | support@milandr.ru |

| Телефон: | +7 495 221-13-55 |