New products

About Milandr

JSC «ICC Milandr» is a Russian privately owned company with headquarters in Moscow (Zelenograd), Russia and subsidiaries in Nizhniy Novgorod, Voronezh, Ekaterinburg, Kazan, Novosibirsk and Solnechnogorsk. The company began in 1993 with a few people and developed into the leading technologically advanced company with a staff of over 600 people, and still growing.

Milandr News

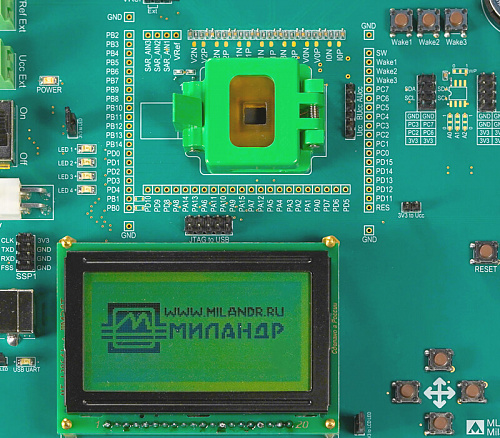

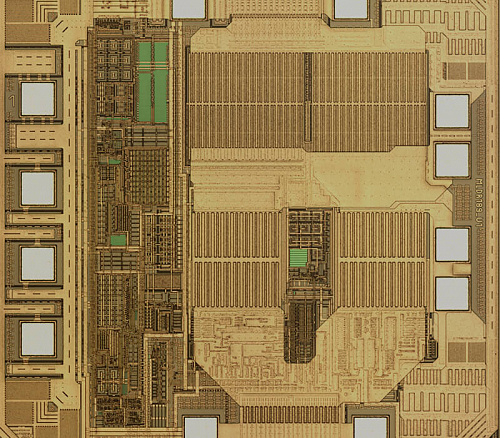

Russian microcontroller K1986BK025 (MDR32F02FI) based on the RISC-V processor core for smart electricity meters

RS485 — a standard for industrial networks.

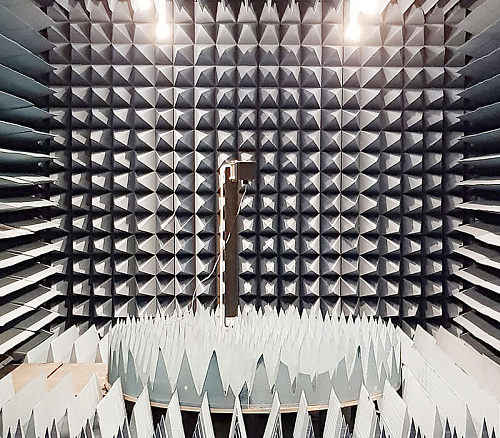

Automotive 77GHz and 24GHz radar systems

If you are looking for a business partner for your project, do not look any further, let’s get in touch