# Ошибки в микросхемах K1986BE1QI

Дата документа: 22/10/25

Настоящий документ содержит описание всех ошибок, выявленных в микросхемах K1986BE1QI, на момент создания данной версии документа.

Дата документа: 22/10/25

## Статус документа

Настоящий документ является НЕКОНФИДЕНЦИАЛЬНЫМ.

## Адрес в сети Интернет

http://www.milandr.ru

## Обратная связь по продукту

Если у Вас есть какие-либо комментарии или предложения по данному продукту, свяжитесь с Вашим поставщиком, указав:

- название продукта;

- комментарии, либо краткое описание Ваших предложений;

- предпочтительный способ связи с Вами и контакты (организация, электронная почта, номер телефона).

## Обратная связь по документу

Если у Вас есть какие-либо комментарии или предложения по данному документу, пожалуйста, пришлите их на электронную почту support@milandr.ru, указав:

- название документа;

- номер и/или дата документа;

- номер страницы;

- комментарии, либо краткое описание Ваших предложений;

- предпочтительный способ связи с Вами и контакты (организация, электронная почта, номер телефона).

# Оглавление

Дата документа: 22/10/25

| Обзор                                                                                                           | 5  |

|-----------------------------------------------------------------------------------------------------------------|----|

| Категории ошибок                                                                                                | 5  |

| Сводная таблица ошибок                                                                                          | 6  |

| Ошибки категории 1                                                                                              |    |

| 0011 Ошибка системного таймера                                                                                  |    |

| Ошибки категории 2                                                                                              | 9  |

| 0014 Возникновение Hard Fault в режиме run time при отображении содержимого периферии                           | 9  |

| 0024 Возникновение ошибки GAPERR в режиме ОУ контроллера ГОСТ Р 52070-2003                                      |    |

| 0025 Ограничение совместимости контроллера передатчика ГОСТ 18977-79 с<br>РТМ 1495-75 (изменение №3) и ARINC429 |    |

| 0026 Сбой выходной тактовой частоты PLL при резком изменении питания в предела                                  |    |

| допустимого                                                                                                     |    |

| 0027 Несоответствие контроллера МКИО в режиме ОУ ГОСТ Р 51765-2001                                              |    |

| 0028 Зависание входа прерывания от батарейного домена контроллера NVIC                                          |    |

| 0030 Формирование высокого потенциала на выводах портов при смене направления                                   |    |

| передачи данных                                                                                                 |    |

| 0031 Отсутствие записи в область данных контроллера Ethernet в режиме Stand Alone                               |    |

| или Stand Alone3                                                                                                |    |

| Ошибки категории 3                                                                                              |    |

| 0002 Невозможность выключить генератор HSI при нулевом ALRF                                                     |    |

| 0003 Немаскируемый запрос передачи DMA от контроллера АЦП                                                       |    |

| 0007 Ошибка верификации запрограммированных данных                                                              |    |

| 0010 Ошибка тактирования МАС-контроллера                                                                        |    |

| 0017 Ошибка арбитража в контроллере CAN                                                                         |    |

| 0018 Чтение регистра RTC_PRL после сброса                                                                       |    |

| 0019 Ошибка приема управляющих пакетов Ethernet                                                                 |    |

| 0020 Ошибка формирования деления частоты CPU_C3, USB_C3, ADC_C3, HSI_C1 и HSE_C1                                |    |

| 0021 Ограничения при работе буферов контроллера Ethernet в автоматическом режим                                 |    |

| режиме FIFO                                                                                                     |    |

| 0022 Ошибка шины АНВ Ethernet-контроллера                                                                       |    |

| 0023 Искажение поля ID принимаемого пакета при арбитраже в блоке CAN                                            | 27 |

| 0029 Время ожидание КШ ответного слова от ОУ менее 14 мкс                                                       |    |

| 0032 Переполнение счетчика ошибок RX_ERR_CNT контроллера CAN                                                    |    |

| 0033 Инверсия передаваемых данных в режиме 10Base-T HD/FD после сброса                                          | ,  |

| Ethernet PHY                                                                                                    | 30 |

| 0034 Пропуск канала АЦП при последовательном преобразовании нескольких канало после выключения АЦП              | ЭB |

| 0035 Остановка счета IWDG при отсутствии частоты PCLK в процессе перезагрузки                                   | 52 |

| значения таймера или обновления значения предделителя                                                           | 33 |

| 3начения таимера или ооновления значения предделителя                                                           |    |

| операций записи и чтения двухпортовой памяти контроллера по ГОСТ 18977-79                                       | €, |

| реализующей приемный буфер, в режиме прямого доступа к памяти                                                   |    |

| 0037 Пропуск секундного импульса при использовании калибровки RTC_CLK                                           | 35 |

| Дата документа: 22/10/25   | K1986BE1QI Errata Notice |

|----------------------------|--------------------------|

| Лист регистрации изменений | 37                       |

# Обзор

Настоящий документ содержит описание ошибок в продукте с указанием категории критичности. Каждое описание содержит:

- уникальный идентификатор ошибки;

- текущий статус ошибки;

Дата документа: 22/10/25

- где существует отклонение от спецификации и условия, при которых возникает ошибка;

- последствия возникновения ошибки в типичных применениях;

- ограничения, рекомендации и способы обхода ошибки, где это возможно.

# Категории ошибок

Ошибки разделены на три категории критичности:

## Категория 1.

Ошибочное поведение, которое невозможно обойти. Ошибки данной категории серьезно ограничивают использование продукта во всех или в большинстве приложений, что делает устройство непригодным для использования.

## Категория 2.

Ошибочное поведение, которое противоречит требуемому поведению. Ошибки данной категории могут ограничивать или серьезно ухудшать целевое использование указанных функций, но не делают продукт непригодным для использования во всех или в большинстве приложений.

## Категория 3.

Ошибочное поведение, которое не было изначально определено, но не вызывает проблем в приложениях при соблюдении рекомендаций.

# Сводная таблица ошибок

В таблице указывается, в каких версиях микросхем присутствует ошибка. Для обозначения ошибки используются следующие символы:

- «Х» - ошибка присутствует;

Дата документа: 22/10/25

- «X\*» - ошибка исправлена частично или видоизменилась.

Версия микросхем определяется датой изготовления, указанной на крышке корпуса микросхемы в формате  $\Gamma\Gamma$  н. где  $\Gamma\Gamma$  – год изготовления,  $\Pi$  – неделя изготовления.

| ID   |                                                                                                                                                                                                          | Микросхемы, изготавливаемые<br>с даты |                  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|--|--|--|--|

|      | Описание                                                                                                                                                                                                 | 1401<br>(рев. 4)                      | 1645<br>(рев. 6) |  |  |  |  |

| Кат  | гегория 1                                                                                                                                                                                                |                                       |                  |  |  |  |  |

| 0011 | Ошибка системного таймера                                                                                                                                                                                | X                                     | X                |  |  |  |  |

| Кат  | гегория 2                                                                                                                                                                                                |                                       |                  |  |  |  |  |

| 0014 | Возникновение исключительной ситуации Hard Fault при динамическом обновлении окон 4 Memory Window и Watch Window содержащих значения памяти или регистров периферии в отладочном режиме запуска run time |                                       |                  |  |  |  |  |

| 0024 | 4 Ошибка GAPERR в режиме ОУ контроллера X                                                                                                                                                                |                                       |                  |  |  |  |  |

| 0025 | Ограничение совместимости контроллера<br>5 передатчика ГОСТ 18977-79 с РТМ 1495-75 X<br>(изменение №3) и ARINC429                                                                                        |                                       |                  |  |  |  |  |

| 0026 | Сбой выходной тактовой частоты PLL при X просадке питания                                                                                                                                                |                                       |                  |  |  |  |  |

| 0027 | Несоответствие контроллера МКИО в режиме ОУ ГОСТ Р 51765-2001                                                                                                                                            |                                       |                  |  |  |  |  |

| 0028 | Зависание входа прерывания от батарейного X X домена контроллера NVIC                                                                                                                                    |                                       |                  |  |  |  |  |

| 0030 | Формирование высокого потенциала на выволах                                                                                                                                                              |                                       |                  |  |  |  |  |

| 0031 | Отсутствие записи в область данных контроллера Ethernet в режиме Stand Alone1 или Stand Alone3                                                                                                           |                                       |                  |  |  |  |  |

| Кат  | гегория 3                                                                                                                                                                                                |                                       | <u>'</u>         |  |  |  |  |

| 0002 | 002 Невозможность выключить генератор HSI при X                                                                                                                                                          |                                       |                  |  |  |  |  |

| 0003 | Немаскируемый запрос передачи DMA от X контроллера АЦП                                                                                                                                                   |                                       |                  |  |  |  |  |

| ID   |                                                                                                                                                                                                                   | Микросхемы, изготавливаемые<br>с даты |                  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|--|

|      | Описание                                                                                                                                                                                                          | 1401<br>(рев. 4)                      | 1645<br>(рев. 6) |  |

| 0007 | Ошибка верификации запрограммированных данных                                                                                                                                                                     | X                                     | X                |  |

| 0010 | Ошибка тактирования МАС контроллера                                                                                                                                                                               | X                                     | X                |  |

| 0017 | Ошибка арбитража в контроллере CAN                                                                                                                                                                                | X                                     |                  |  |

| 0018 | Чтение регистра RTC_PRL после сброса                                                                                                                                                                              | X                                     | X                |  |

| 0019 | Ошибка приема управляющих пакетов Ethernet                                                                                                                                                                        | X                                     |                  |  |

| 0020 | Ошибка формирования деления частоты CPU_C3, USB_C3, ADC_C3, HSI_C1 и HSE_C1                                                                                                                                       | X                                     | X*               |  |

| 0021 | Ограничения при работе буферов Ethernet контроллера в автоматическом режиме и режиме FIFO                                                                                                                         | X                                     |                  |  |

| 0022 | Ошибка шины AHB Ethernet контроллера                                                                                                                                                                              | X                                     |                  |  |

| 0023 | Искажение поля ID принимаемого пакета при арбитраже в блоке CAN                                                                                                                                                   | X                                     |                  |  |

| 0029 | Время ожидание КШ ответного слова от ОУ менее 14 мкс                                                                                                                                                              | X                                     |                  |  |

| 0032 | Переполнение счетчика ошибок RX_ERR_CNT контроллера CAN                                                                                                                                                           | X                                     | X                |  |

| 0033 | Инверсия передаваемых данных в режиме 10Base-T HD/FD после сброса Ethernet PHY                                                                                                                                    | X                                     | X                |  |

| 0034 | Пропуск канала АЦП при последовательном преобразовании нескольких каналов после выключения АЦП                                                                                                                    | X                                     | X                |  |

| 0035 | Остановка счета IWDG при отсутствии частоты PCLK в процессе перезагрузки значения таймера или обновления значения предделителя                                                                                    | X                                     | X                |  |

| 0036 | Негарантированное чтение достоверных данных при одновременном выполнении операций записи и чтения двухпортовой памяти контроллера по ГОСТ 18977-79, реализующей приемный буфер, в режиме прямого доступа к памяти | X                                     | X                |  |

| 0037 | Пропуск секундного импульса при использовании калибровки RTC_CLK                                                                                                                                                  | X                                     | X                |  |

# Ошибки категории 1

Дата документа: 22/10/25

## 0011 Ошибка системного таймера

## Статус

Будет исправлена только в случае замены ядра.

#### Описание

В случае работы на частотах более 25 МГц с ненулевой задержкой Delay[2:0] в регистре EEPROM\_CMD системный таймер останавливает счет во время чтения новых инструкций из флэш-ускорителя, что приводит к увеличению времени счета.

#### **Условия**

Значения разрядов Delay регистра EEPROM\_CMD отличны от нуля.

#### Последствия

Увеличение времени счета системного таймера.

## Рекомендации и способы обхода

При работе на больших частотах использовать таймеры периферии вместо системного таймера.

## Ошибки категории 2

Дата документа: 22/10/25

# 0014 Возникновение Hard Fault в режиме run time при отображении содержимого периферии

## Статус

Проводятся исследования.

#### Описание

При отладке программы в режиме run time с одновременным динамическим обновлением окон Memory Window и Watch Window, содержащих значения памяти или регистров периферии, возникает исключительная ситуация Hard Fault.

#### Условия

Выход отладочной системы на шину АНВ для чтения содержимого внешней периферии.

#### Последствия

Возникновение исключительной ситуации Hard Fault.

## Рекомендации и способы обхода

При использовании среды Phyton никаких действий не требуется, недостаток учтен в среде разработки программ. При использовании других средств разработки (например, Keil) закрывать окна Watch и Memory, если они отображают содержимое внешней периферии при запуске в run time.

# 0024 Возникновение ошибки GAPERR в режиме ОУ контроллера ГОСТ Р 52070-2003

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

После успешного завершения приема или передачи сообщения оконечным устройством в последующей паузе t2 < 6 мкс (согласно ГОСТ Р 52070-2003 t2 < 4 мкс) приход синхросигнала вызывает ошибку GAPERR.

#### **Условия**

Возникновение синхросигнала в паузе t2 < 6 мкс после успешного завершения предыдущего сообщения оконечным устройством.

#### Последствия

При установленном бите RERR регистра контроля командное слово, получаемое при установленном флаге GAPERR, не принимается и не отрабатывается оконечным устройством.

#### Рекомендации и способы обхода

Всегда устанавливать бит RERR регистра контроля в «0» для автоматического сброса ошибки GAPERR при переходе оконечного устройства в состояние IDLE. В этом случае прием командного слова с синхросигналом, полученным в паузе t2 < 6 мкс, будет приниматься и отрабатываться оконечным устройством корректно.

# 0025 Ограничение совместимости контроллера передатчика ГОСТ 18977-79 с PTM 1495-75 (изменение №3) и ARINC429

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

При передаче данных в RZ последовательном коде на скорости 100 Кбит/с в соответствии с ГОСТ 18977-79 длительности импульсов положительной и отрицательной полярности наличия сигнала составляют 4 мкс. Это ограничивает совместимость с руководством РТМ 1495-75 (изменение №3) и стандартом ARINC429, в которых эта длительность регламентирована как 5 мкс  $\pm$  5 %.

#### **Условия**

При передаче со скоростью 100 Кбит/с.

#### Последствия

При чувствительности принимающего устройства, функционирующего в соответствии с руководством РТМ 1495-75 (изменение №3) или стандартом ARINC429, к длительности импульса положительной или отрицательной полярности наличия сигнала длительностью не менее 5 мкс  $\pm$  5 % (при скорости передачи 100 Кбит/с) возможен сбой.

#### Рекомендации и способы обхода

При сопряжении с устройствами на скорости 100 Кбит/с, соответствующими РТМ 1495-75 (изменение №3) или ARINC429, требуется проверка на отсутствие сбойных ситуаций принимающим устройством.

# 0026 Сбой выходной тактовой частоты PLL при резком изменении питания в пределах допустимого

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

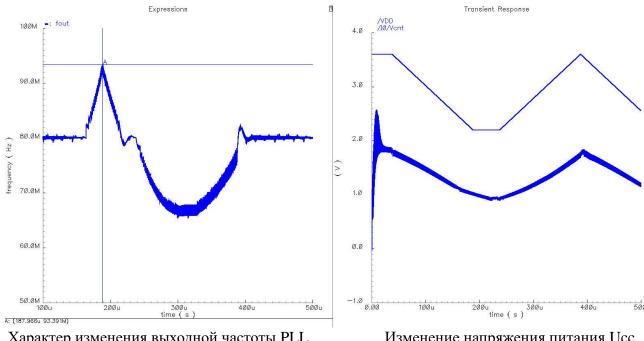

При просадке питания со скоростью большей, чем 5 В/мс происходит увеличение выходной тактовой частоты с PLL с последующим возвращением к расчетному значению. При аналогичном скачке напряжения питания вверх происходит уменьшение выходной тактовой частоты PLL с последующим возвращением к расчетному значению.

| Скорость изменения напряжения питания Ucc, B/мс | Длительность фронта изменения напряжения питания Ucc, мкс | Изменение амплитуды напряжения питания Ucc, B | Входная частота PLL, МГц | Коэф.<br>умножения<br>PLL | Изменение выходной частоты PLL, МГц |

|-------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------|--------------------------|---------------------------|-------------------------------------|

| 5,0                                             | 280                                                       | $3,6 \rightarrow 2,2$                         | 16                       | 5                         | $80 \rightarrow 82$                 |

| 7,7                                             | 180                                                       | $3,6 \rightarrow 2,2$                         | 16                       | 5                         | $80 \rightarrow 92$                 |

| 9,3                                             | 150                                                       | $3,6 \rightarrow 2,2$                         | 16                       | 5                         | $80 \rightarrow 103$                |

| 11,6                                            | 120                                                       | $3,6 \rightarrow 2,2$                         | 16                       | 5                         | 80 → 119                            |

|                                                 |                                                           |                                               |                          |                           |                                     |

| 9,3                                             | 9,3 150                                                   |                                               | 10                       | 8                         | $80 \rightarrow 94$                 |

| 11,6                                            | 120                                                       | $3,6 \rightarrow 2,2$                         | 10                       | 8                         | $80 \rightarrow 106$                |

| 70                                              | 70 20                                                     |                                               | 10                       | 8                         | $80M \rightarrow 220$               |

|                                                 |                                                           |                                               |                          |                           |                                     |

| 11,6                                            | 11,6 120 $3,6 \rightarrow 2,2$                            |                                               | 5                        | 16                        | $80 \rightarrow 86$                 |

| 14                                              | 14 100 3,6                                                |                                               | 5                        | 16                        | $80 \rightarrow 98$                 |

|                                                 |                                                           |                                               |                          |                           |                                     |

| 30                                              | 30 20 3,6                                                 |                                               | 16                       | 9                         | $144 \rightarrow 189$               |

| 30                                              | 20                                                        | $3,6 \rightarrow 3,0$                         | 16                       | 5                         | $80 \rightarrow 102$                |

| 30                                              | 20                                                        | $3,6 \rightarrow 3,0$                         | 10                       | 8                         | 80 → 102                            |

| 30                                              | 20                                                        | $3,6 \rightarrow 3,0$                         | 9                        | 16                        | 144 → 193                           |

| 30                                              | 20                                                        | $3,6 \rightarrow 3,0$                         | 5                        | 16                        | $80 \rightarrow 97$                 |

Характер изменения выходной частоты PLL (80 МГц = 10 МГц • 8) при резком изменении напряжения питания

Изменение напряжения питания Ucc (на рисунке верхняя линия) с уровня 3,6 до 2,2 В за 150 мкс и обратно

## **Условия**

Изменение напряжения питания в предельно-допустимом диапазоне со скоростью более 5 В/мс. Чем больше скорость изменения напряжения питания, тем больше изменение выходной частоты. Чем больше входная частота, тем больше изменение выходной частоты. Чем больше коэффициент умножения, тем больше изменение выходной частоты

#### Последствия

Увеличение или уменьшение тактовой частоты от расчетного значения. При этом возможно появление частот, превышающих максимально допустимое значение рабочей частоты и нарушение времени выборки из Flash.

## Рекомендации и способы обхода

В реальной жизни изменение напряжения питания с такими скоростями маловероятны. Но при возможности возникновения такого рода сбоев рекомендуется увеличить емкости по питанию и установить большее, чем требуется время задержки при выборке из Flash.

## 0027 Несоответствие контроллера МКИО в режиме ОУ ГОСТ Р 51765-2001

## Статус

Исправлено в микросхемах с 1645. Смотри рекомендации и способы обхода.

#### Описание

Дата документа: 22/10/25

В случае применения контроллера МКИО в режиме ОУ в условиях, описанных в пунктах 5.2.2, 5.2.3, 5.2.5, 6.1.1.2, 6.1.4, 6.1.7.1, 6.1.8, 6.2.5.2, 7.1 поведение контроллера не соответствует требованиям ГОСТ Р 51765-2001.

#### **Условия**

- 5.2.2 Отклонение переходов входного сигнала через нулевой уровень  $\geq \pm 150$  нс.

- 5.2.3 Изменение размаха амплитуды входного сигнала 0,86 В для трансформаторного включения (1,2 В для прямого включения).

- 5.2.5 Подавление синфазных помех.

- 6.1.1.2 Недопустимое сочетание кодов полей КС.

- 6.1.4 Команды замещения.

- 6.1.7.1 Превышение времени тайм-аута при приеме информации в формате ОУ-ОУ.

- 6.1.8 Переключение шины данных с основной на резервную и обратно.

- 6.2.5.2 Ошибка длины массива слов данных в формате КШ ОУ.

- 7.1 Прием сообщений при воздействии белого шума.

#### Последствия

Недопустимое поведение ОУ, не соответствующее ГОСТ Р 51765-2001.

#### Рекомендации и способы обхода

Пункт 7.1 не выполняется для приемопередатчика 5559ИН13. Пункт 6.1.8 выполняется нестабильно для приемопередатчика 5559ИН67Т.

## 0028 Зависание входа прерывания от батарейного домена контроллера NVIC

## Статус

Будет исправлено в следующей версии продукта.

#### Описание

Дата документа: 22/10/25

Сигнал прерывания от батарейного домена формируется асинхронно по отношению к частоте тактирования ядра микросхемы. При возникновении прерывания на входе IRQ27 (прерывание от BKP и часов реального времени) возможно зависание входа и, как следствие, отсутствие возникновения прерывания.

#### **Условия**

Установка активного уровня прерывания от ВКР и часов реального времени может совпасть с фронтом синхросигнала тактирования ядра микросхемы, что приведет к зависанию входа прерывания.

#### Последствия

Невозможность в дальнейшем получать и обрабатывать прерывания от ВКР и часов реального времени.

### Рекомендации и способы обхода

В основном теле программы предусмотреть запрет прерывания от RTC с помощью бит 3-5 регистра RTC\_CS, в случае превышения счетчиком часов реального времени границы сравнения, а затем повторно разрешить прерывание. Эти действия приведут к переключению входного сигнала прерывания контроллера NVIC в неактивное состояние, что возобновит корректную работу входа прерываний. Либо не использовать прерывание от RTC, а осуществлять опрос бит 0-2 регистра RTC\_CS в основном цикле программы с дальнейшей их обработкой.

# 0030 Формирование высокого потенциала на выводах портов при смене направления передачи данных

## Статус

Исследование.

#### Описание

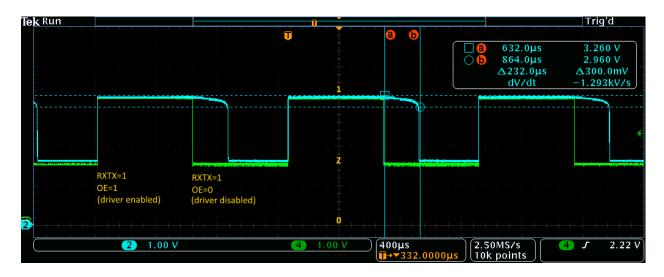

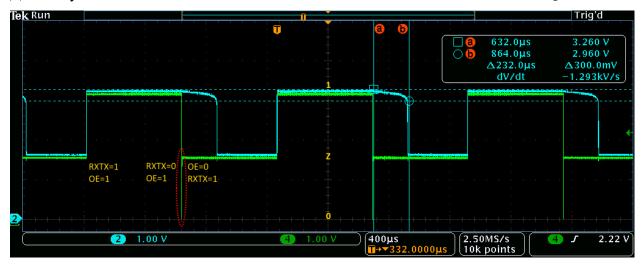

Если пользовательский вывод сконфигурирован на выход и выдает логическую «1», то при смене направления передачи данных (ОЕ) с выхода на вход, вместо ожидаемого высокоимпедансного состояния на выводе ошибочно формируется высокий потенциал.

Время переключения выходного драйвера ТХ в неактивное состояние зависит от номинала подключенной нагрузки к порту. Ниже на диаграмме представлен переход выходного драйвера из активного в неактивное состояние при нагрузках (pullup = pulldown) 1 кОм (канал 4) и 15 кОм (канал 2) в нормальных условиях.

Канал 4 (Зеленый) – нагрузка 1 кОм (ожидаемое поведение с высокоомной нагрузкой) Канал 2 (Синий) – нагрузка 15 кОм (затянутый фронт переключения)

## Условия

Всегда.

#### Последствия

Нет.

#### Рекомендации и способы обхода

Перевести драйвер ТХ на выдачу логического «0». Дождаться появление логического «0» на входе цифрового приемника RX путем опроса регистра RXTX и перевести драйвер в неактивное состояние (OE=0).

Не рекомендуется выравнивать фронт переключения путем установки дополнительной нагрузки на вывод порта.

Канал 4 (Зеленый) – нагрузка 15 кОм (с рекомендацией) Канал 2 (Синий) – нагрузка 15 кОм (затянутый фронт переключения)

# 0031 Отсутствие записи в область данных контроллера Ethernet в режиме Stand Alone1 или Stand Alone3

## Статус

Проводятся исследования.

Дата документа: 22/10/25

#### Описание

В режиме Stand Alone1 или Stand Alone3 запись данных управляющим устройством в буферную область памяти контроллера Ethernet может не происходить.

#### **Условия**

Режим работы микросхемы Stand Alone1 или Stand Alone3 с доступом к блоку контроллера Ethernet. Запись данных по интерфейсу SRAM в контроллер Ethernet.

## Последствия

Потеря данных, подготовленных для передачи. Невозможность использовать контроллер Ethernet.

## Рекомендации и способы обхода

Использовать контроллер Ethernet только в линейном режиме работы буферов. После каждой записи в буферную память выполнять верификацию записанных данных и, в случае неудачи, повторять процедуру записи. При программной инициализации режима Stand Alone1 или Stand Alone3, рекомендуется устанавливать частоту ядра  $HCLK = Ethernet\ MAC = 50\ M\Gamma$ ц, что позволяет снизить процент не записи данных с первого раза.

# Ошибки категории 3

Дата документа: 22/10/25

## 0002 Невозможность выключить генератор HSI при нулевом ALRF

## Статус

Проводятся исследования.

#### Описание

Бит разрешения работы HSION регистра BKP\_REG\_0F батарейного домена может быть сброшен в «0» только при взведенном в «1» флаге ALRF часов реального времени. При сбросе флага ALRF в «0» бит разрешения работы HSION устанавливается в «1», что приводит к включению генератора HSI.

#### **Условия**

Всегда.

#### Последствия

Невозможность отключить генератор, повышенное потребление.

## Рекомендации и способы обхода

Для отключения генератора HSI необходимо убедится, что микросхема тактируется другим источником синхросигнала, взвести бит ALRF и после этого сбросить бит HSION.

Дата документа: 22/10/25

## 0003 Немаскируемый запрос передачи DMA от контроллера АЦП

## Статус

В микросхемах до 1645 сигнал dma\_done, формируемый посредством АЦП, не вызывает прерывание, поэтому обработку АЦП нельзя вести через прерывание DMA.

В микросхемах с 1645 сигнал dma\_done, формируемый посредством АЦП, вызывает прерывание, поэтому обработку АЦП вести через прерывание DMA можно.

#### Описание

В качестве запроса передачи по DMA контроллером АЦП используется сигнал окончания преобразования EOCIF. Вне зависимости от настроек контроллера DMA и контроллера АЦП этот запрос приходит на контроллер DMA. Если DMA контроллер настроен на обработку этого запроса, то он обработает этот запрос, если же не настроен, то обработки не будет, но контроллер DMA взведет сигнал dma\_done (прерывание от DMA) и тем самым запросит обработку прерывания от DMA.

#### **Условия**

Всегда.

## Последствия

При работе контроллера АЦП и DMA возникают запросы прерываний от DMA контроллера указывающие, что был запрос передачи по каналу АЦП, но он не был обработан.

## Рекомендации и способы обхода

В микросхемах до 1645 никаких действий не требуется.

В микросхемах с 1645 для блокировки сигнала dma\_done формируемого посредством АЦП необходимо блокировать запрос SREQ с помощью следующей команды:

$DMA \rightarrow CHNL\_USEBURST\_SET = 1 << 30.$

## 0007 Ошибка верификации запрограммированных данных

## Статус

Исследование.

Дата документа: 22/10/25

#### Описание

После изменения данных во Flash-памяти верификация записанных данных может завершаться с ошибкой, так как считанные данные могут содержать старые данные, сохраненные в буфере Flash-ускорителя.

#### Условия

Если инструкция чтения LDR не выровнена на 4, то обновление буфера Flash-ускорителя не происходит.

#### Последствия

Не происходит обновление буфера Flash-ускорителя, что может приводить к чтению старых ланных.

## Рекомендации и способы обхода

Для обновления буфера Flash-ускорителя необходимо выполнить 5 чтений Flash-памяти с декрементом адреса по 0x10, при этом инструкция чтения LDR должна быть выровнена на 4. После этого инструкция чтения LDR в процедуре верификации не обязательно должна быть выровнена на 4, так как буфер Flash-ускорителя уже обновлен. Функция обновления буфера Flash-ускорителя приведена в библиотеке SPL.

# 0010 Ошибка тактирования МАС-контроллера

## Статус

Проводятся исследования.

Дата документа: 22/10/25

#### Описание

При тактировании МАС-контроллера частотой меньшей, чем частота ядра, возникают сбои при записи в регистры и память данных МАС-контроллера.

#### Условия

Всегда.

## Последствия

Регистр или память не принимают нужного значения после записи.

## Рекомендации и способы обхода

Тактировать МАС-контроллер частотой равной частоте ядра, не задавая делителей.

# 0017 Ошибка арбитража в контроллере САП

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

При выходе на линию CAN двух контроллеров, и при этом у второго контроллера больший приоритет по ID, возникает ситуация, при которой первый контроллер отпускает линию, так как проиграл арбитраж (имеет меньший приоритет), но второй формирует на шине ошибку BIT STAFF ERROR, FRAME ERROR или CRC ERROR.

#### Условия

Если первый контроллер с меньшим приоритетом вышел на ~1 TQ ранее второго контроллера с большим приоритетом.

## Последствия

После возникновения ошибки оба контроллера повторяют свои передачи, но при этом во время ошибки они синхронизируются, и повторная передача выполняется без расхождения в 1 ТQ. В этом случае арбитраж производится корректно, и оба контроллера передают свои пакеты без ошибок.

## Рекомендации и способы обхода

Учитывать при разработке ПО при анализе ошибок на шине CAN. При увеличении траффика по шине CAN вероятность такой ошибки снижается, так как все передатчики постоянно синхронизируются.

# 0018 Чтение регистра RTC\_PRL после сброса

#### Статус

Проводятся исследования.

#### Описание

После сброса в регистре RTC\_PRL всегда считываются нули, независимо от ранее записанного в него значения. Реально регистр сбрасывается только при исчезновении питания батарейного домена BUcc.

#### Условия

Всегда.

#### Последствия

Не выявлено.

## Рекомендации и способы обхода

# 0019 Ошибка приема управляющих пакетов Ethernet

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

При приеме пакета с адресом отправителя/получателя равным 0х8808 происходит частичная потеря пакета.

#### Условия

При  $CF_EN = 0$  в регистре  $R_CFG$ .

#### Последствия

Потеря пакета.

## Рекомендации и способы обхода

Всегда устанавливать бит  $CF_EN = 1$  в регистре  $R_CFG$ . Учитывать при разработке  $\Pi O$  прием управляющих пакетов.

# 0020 Ошибка формирования деления частоты CPU\_C3, USB\_C3, ADC\_C3, HSI\_C1 и HSE\_C1

#### Статус

Исследование.

#### Описание

Изменение дополнительного коэффициента деления при формировании частоты CPU\_C3 (поле CPU\_C3\_SEL), частоты USB\_C3 (поле USB\_C3\_SEL), частоты ADC\_C3 (поле ADC\_C3\_SEL), частоты HSI\_C1 (поле HSI\_C1\_SEL) и частоты HSE\_C1 (поле HSE\_C1\_SEL) возможно осуществлять только в большую сторону. Уменьшение коэффициента деления приводит к прекращению формирования тактового сигнала. Сброс настройки возможен только через сигнал сброса всей микросхемы.

#### **Условия**

Уменьшение коэффициента деления.

#### Последствия

Делитель не формирует выходной тактовый сигнал.

#### Рекомендации и способы обхода

Учитывать при разработке ПО.

В микросхемах, изготовленных с 1645, возможно уменьшение коэффициента деления путем его последовательного изменения с шагом 1 и с временным интервалом не менее T (где T — это длительность двух периодов выходной частоты делителя до изменения коэффициента деления).

# 0021 Ограничения при работе буферов контроллера Ethernet в автоматическом режиме и режиме FIFO

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

При работе буферов контроллера Ethernet в автоматическом режиме и режиме FIFO ядро не успевает записывать данные в буферы при работе на частоте менее 144 МГц. Поэтому рекомендуется работать на частоте 144 МГц либо записывать дополнительные упреждающие данные. При считывании принятых пакетов в вышеописанных режимах работы буферов не использовать флаг RF\_OK регистра IFR, который может стать неактивным при наличии пакета в буфере. При считывании пакетов использовать условие неравенства указателей R\_Tail и R\_Head.

#### **Условия**

Всегда.

## Последствия

Потеря пакетов.

## Рекомендации и способы обхода

# 0022 Ошибка шины AHB Ethernet-контроллера

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

После операции записи регистров или памяти Ethernet-контроллера нельзя проводить операции чтения/записи с ОЗУ по адресам 0x20100000-0x20103FFF, так как это приводит к ошибочной записи в Ethernet-контроллер. Необходимо дождаться завершения операции записи в Ethernet-контроллер с помощью инструкций «NOP» или инструкций барьерной синхронизации.

#### Условия

Всегда.

## Последствия

Ошибочная запись в Ethernet-контроллер.

## Рекомендации и способы обхода

## 0023 Искажение поля ID принимаемого пакета при арбитраже в блоке CAN

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

При одновременном выполнении передачи и приема пакетов контроллером CAN (выполняется процедура арбитража), если у стандартных пакетов обнаруживается различие в последнем бите идентификатора или в бите RTR, а у расширенных пакетов — различие в последнем бите 11-битного идентификатора, в любом бите 18-битного идентификатора, в бите SRR, в бите IDE или в бите RTR, и при этом передаваемый пакет имеет меньший приоритет («проигрывает» арбитраж), то у принимаемого пакета («выигравшего» арбитраж) происходит искажение поля ID. Это вызвано тем, что до момента проигрыша арбитража контроллер CAN считает, что именно он осуществляет передачу и не сохраняет ID принимаемого сообщения (остаются данные от предыдущих пакетов).

#### **Условия**

«Проигрыш» арбитража в последнем бите идентификатора или в бите RTR у стандартных пакетов.

«Проигрыш» арбитража в последнем бите 11-битного идентификатора, в любом бите 18-битного идентификатора, в бите SRR, в бите IDE или в бите RTR у расширенных пакетов.

#### Последствия

Искажение поля ID у принимаемого пакета, который «выиграл» арбитраж.

#### Рекомендации и способы обхода

Разрешить примем собственных пакетов (бит ROP = 1) с их последующим игнорированием в ходе программной обработки. В этом случае при арбитраже принимаемые пакеты не искажаются.

## 0029 Время ожидание КШ ответного слова от ОУ менее 14 мкс

## Статус

Исправлено в микросхемах с 1645.

Дата документа: 22/10/25

#### Описание

Не выполняется п.4.5.3.3 ГОСТ Р 52070-2003 время ожидания КШ поступления ОС t1, по истечении которого он должен зафиксировать отсутствие ОС от ОУ, должно быть не менее 14 мкс.

#### **Условия**

Всегда.

#### Последствия

Фиксация отсутствия ОС от ОУ.

## Рекомендации и способы обхода

Алгоритм обхода:

- 1 отправка КС;

- 2 ожидание завершения отправки КС;

- 3 выключение тактирование блока МКИО (RST CLK -> ETH CLOCK, 25 бит);

- 4 ожидание 2 мкс (отсчет с помощью таймера);

- 5 включение тактирование блока МКИО (RST CLK -> ETH CLOCK, 25 бит);

- 6 прием ОС.

## 0032 Переполнение счетчика ошибок RX ERR CNT контроллера CAN

## Статус

Будет исправлено в следующей версии продукта.

#### Описание

Дата документа: 22/10/25

В случае, если контроллер CAN постоянно обнаруживает ошибки при приеме данных, то счетчик ошибок приема RX\_ERR\_CNT будет инкрементироваться до верхнего предела (0x1FF), после чего он должен остановиться. Однако, этого не происходит – счетчик после приема очередного кадра с ошибкой переполняется и сбрасывается в 0x000. Из-за этого контроллер CAN, ранее находившийся в пассивном к ошибкам состоянии ERROR PASSIVE (RX\_ERR\_CNT > 127), ошибочно переходит в активное к ошибкам состояние ERROR ACTIVE и при обнаружении ошибок начинает посылать кадры активной ошибки. Данное поведение не соответствует стандарту, потому что для перехода в активное к ошибкам состояние ERROR ACTIVE контроллеру CAN необходимо успешно принять кадр.

## Условия и причина

При постоянном приеме кадров с ошибкой.

#### Последствия

Ошибочный переход контроллера CAN в активное к ошибкам состояние.

## Рекомендации и способы обхода

Учитывать при разработке аппаратуры.

# 0033 Инверсия передаваемых данных в режиме 10Base-T HD/FD после сброса Ethernet PHY

## Статус

Исследование.

Дата документа: 22/10/25

#### Описание

После снятия сигнала аппаратного сброса nRST с блока Ethernet PHY (переключение бита nRST из «0» в «1» в регистре PHY\_Control) блок передатчика 10Base-T может с небольшой вероятностью (0,5% – 1%) перейти в состояние, в котором все данные, поступающие для передачи от контроллера уровня MAC, будут инвертированы. Импульсы NLP (Normal Link Pulse) при этом не инвертируются, поэтому внешнее принимающее устройство не может автоматически скорректировать полярность принимаемого сигнала.

Инвертирование данных может проявляться в следующих режимах работы блока PHY (регистр PHY\_Control, поле MODE[2:0]): 10Base-T HD (000), 10Base-T FD (001) и полностью автоматический режим (111), если после автосогласования будет установлена скорость обмена данными 10 Мбит/с, режим работы HD или FD.

## Условия и причина

Снятие сигнала аппаратного сброса nRST с блока Ethernet PHY.

## Последствия

Переход блока передатчика 10Base-Т в состояние, в котором все данные, поступающие для передачи от контроллера уровня МАС, инвертируются.

## Рекомендации и способы обхода

Если предполагается работа со скоростью обмена данными 10 Мбит/с (PHY\_Control.MODE[2:0] = 000, 001 или 111), то после снятия сигнала аппаратного сброса nRST с блока Ethernet PHY необходимо проверить, инвертируются ли передаваемые данные, и при необходимости выполнить повторный сброс Ethernet PHY с помощью бита nRST в регистре PHY\_Control. Для проверки передаваемых данных можно воспользоваться тестовым режимом КЗ блока PHY (в данном режиме передаваемые данные возвращаются обратно блоку MAC, на линию данные не передаются).

#### Алгоритм обхода:

- 1 в регистре PHY\_Control установить требуемый режим работы PHY в поле MODE[2:0] и установить бит nRST = 0;

- 2 выдержать паузу не менее 100 мкс, после чего установить бит nRST = 1;

- 3 выдержать паузу не менее 16 мс для выхода блока PHY в рабочий режим, после чего дождаться установки бита READY в «1» в регистре PHY Status;

- 4 по интерфейсу MDIO считать регистр управления (0) и сохранить полученное значение;

- 5 выполнить программный сброс PHY (уменьшает вероятность перехода передатчика 10Base-Т в ошибочное состояние): в считанном значении (п. 4) установить в «1» бит 15 Reset, после чего записать модифицированное значение в регистр управления (0). Дождаться, когда бит 15 Reset в регистре управления (0) аппаратно сбросится в «0»;

- 6 перевести блок PHY в режим 10Base-T FD и установить режим K3: по интерфейсу MDIO записать в регистр управления (0) значение 0х4100;

- 7 выполнить инициализацию блока Ethernet MAC, дополнительно установив в регистре

Дата документа: 22/10/25

R\_CFG биты AC\_EN, EF\_EN и SF\_EN;

- 8 выполнить отправку двух пакетов размером 60 байт с тестовыми данными: первые шесть байт -0xFF, остальные данные -0xAA55AA55;

- 9 дождаться получения одного пакета, после чего по полю состояния приема пакета выполнить проверку:

- а пакет принят с ошибкой CRC или SF (инвертированный пакет) перейти к п. 1;

- б пакет принят успешно перейти к п. 10.

- 10 выполнить деинициализацию блока Ethernet MAC;

- 11 восстановить значение в регистре управления (0), сохраненное в п. 4;

- 12 блок РНҮ готов к работе.

Время выполнения одного цикла алгоритма обхода составляет порядка 17 мс:

100 мкс (аппаратный сброс РНҮ) + 16 мс (выход РНҮ в рабочий режим) +

300 мкс (программный сброс РНУ) + 140 мкс (передача двух пакетов) +

20 мкс (исполнение кода при -O0,  $\sim$ 2700 тактов при частоте CPU\_CLK = 140 МГц) +

104 мкс (обращения к PHY по MDIO при частоте MDC = 2,5 М $\Gamma$ ц).

Алгоритм обхода приведен в библиотеке SPL MDR32FxQI, начиная с вер. 1.1.0, файл MDR32FxQI\_eth.c, функция ETH\_CheckMode10BaseT().

# 0034 Пропуск канала АЦП при последовательном преобразовании нескольких каналов после выключения АЦП

#### Статус

Проводятся исследования.

Дата документа: 22/10/25

#### Описание

В режиме последовательного преобразования нескольких каналов в результате отключения АЦП (бит Gfg\_REG\_ADON) при последующем включении АЦП однократно пропускается канал, на котором остановилось преобразование при отключении. Происходит преобразование следующего канала, участвующего в последовательном преобразовании.

#### Условия

Включение АЦП после отключения АЦП при последовательном преобразовании нескольких каналов.

#### Последствия

Пропуск преобразования канала АЦП, на котором остановилось преобразование при отключении.

## Рекомендации и способы обхода

После отключения АЦП при использовании последовательного преобразования нескольких каналов:

- 1) Отключить переключение каналов (бит Cfg\_REG\_CHCH).

- 2) Включить переключение каналов только для канала, на котором остановилось преобразование при отключении, и участвующих в преобразовании каналов с бо́льшими номерами (регистр ADC1\_CHSEL).

После включения АЦП:

1) Включить переключение для всех требуемых каналов.

# 0035 Остановка счета IWDG при отсутствии частоты PCLK в процессе перезагрузки значения таймера или обновления значения предделителя

## Статус

Исследование.

Дата документа: 22/10/25

#### Описание

В процессе работы IWDG остановка частоты PCLK блока IWDG после вызова запроса перезагрузки значения таймера через регистр IWDG\_KEY (записью значения 0хАААА) и перед фактическим обновлением значения таймера или после вызова запроса обновления предделителя (запись в регистр IWDG\_PR) и перед фактическим обновлением значение предделителя блокирует сигнал запроса на обновление значения таймера в активном состоянии. В результате чего до повторного появления частоты PCLK или любого сброса сторожевой таймер IWDG не осуществляет счет и не формирует сброс. Так как в случае запроса перезагрузки IWDG непрерывно перезагружается значением перезагрузки, а в случае запроса обновления предделителя — непрерывно осуществляет обновление предделителя. После появления частоты PCLK и фактического обновления соответствующих значений или после любого сброса IWDG восстанавливает процесс счета.

#### **Условия**

Остановка частоты PCLK блока IWDG:

- 1) После вызова запроса перезагрузки значения таймера через регистр IWDG\_KEY (записью значения 0хAAA) и перед фактическим обновлением значения таймера в процессе работы IWDG.

- 2) После вызова запроса обновления предделителя таймера через регистр IWDG\_PR и перед фактическим обновлением предделителя в процессе работы IWDG.

#### Последствия

Отсутствие счета таймера IWDG и формирования им сброса до появления частоты PCLK или любого сброса.

#### Рекомендации и способы обхода

Реализовать в разрабатываемой системе один или несколько из предложенных способов:

- 1) Перед вызовом запроса перезагрузки значения таймера и на время сброса флага RVU, а также перед вызовом запроса обновления предделителя и на время сброса флага PVU, переводить тактирование PCLK (соответствует частоте HCLK) на частоту, которая гарантируется в разрабатываемой системе например, LSI (поскольку наличие частоты LSI обязательно для работы IWDG, в случае её отсутствия IWDG не сбросит систему при любых обстоятельствах).

- 2) Использовать внешний сторожевой таймер.

Дата документа: 22/10/25

0036 Негарантированное чтение достоверных данных при одновременном выполнении операций записи и чтения двухпортовой памяти контроллера по ГОСТ 18977-79, реализующей приемный буфер, в режиме прямого доступа к памяти

## Статус

Учитывать при разработке

### Описание

В случае работы с буфером приемника контроллера по ГОСТ 18977-79 в режиме прямого доступа к памяти (не режим FIFO) при одновременном выполнении операций записи и чтения одной ячейки буфера операция чтения приведет к считыванию некорректных данных

#### **Условия**

В основе приемного буфера FIFO контроллера по ГОСТ 18977-79 находится блок двухпортовой памяти: при работе с данной памятью приоритет всегда у операции записи, поэтому при выполнении транзакций обмена в асинхронных системах, когда одновременно выполнятся операции записи/чтения одной ячейки, операция чтения приведет к чтению недействительных данных

#### Последствия

Чтение недействительных данных из приемного буфера контроллера по ГОСТ 18799-79, работающего в режиме прямого доступа к памяти

#### Рекомендации и способы обхода

- 1. Использовать при работе с приемным каналом режим FIFO

- 2. Разграничить во времени операции чтения/записи буфера приемника

- 3. В программном коде выполнять два чтения одной и той же ячейки приемного буфера подряд с запретом работы блока DMA и прерываний на время этих чтений. Программный код, реализующий данный способ обхода:

*while*(  $(MDR\_DMA->STATUS \& 0x70) != 0);$  // Перед выполнением двух чтений из приемного буфера ожидаем, что все транзакции по DMA завершены;

$MDR\_DMA$ ->CFG &= ~(1 << 0); // Запрет работы DMA на момент двух чтений из приемного буфера;

NVIC\_DisableIRQ(interrupts); // Выключение обработки прерываний на уровне NVIC;

$real = (*(uint32_t*)(0x400D1000+addr); //$  Первое чтение из приемного буфера (в данном случае используется базовый адрес буфера первого приемника) в переменную;

$real = (*(uint32\_t*)(0x400D1000+addr); //$  Второе чтение из приемного буфера в переменную;  $NVIC\_EnableIRQ(interrupts); //$  Включение обработки прерываний на уровне NVIC. Если за время двух чтений был запрос на прерывание, то после исполнения данной строчки кода вызовется его обработчик;

$MDR\_DMA$ ->CFG /= (1 << 0); // Обратное разрешение работы DMA.

## 0037 Пропуск секундного импульса при использовании калибровки RTC CLK

## Статус

Исследование.

Дата документа: 22/10/25

#### Описание

В блоке RTC для формирования частоты SEC\_CLK из частоты RTC\_CLK используется делитель, выполненный на счетчике RTC\_DIV с основанием счета RTC\_PRL. Для калибровки (замедления) RTC\_CLK используется счетчик RTC\_20, который на время RTC\_20 < RTC\_CAL останавливает счет RTC\_DIV.

Во время работы RTC с калибровкой частоты RTC\_CLK (поле RTC\_CAL[7:0] != 0 в регистре REG\_0F) при определенных значениях RTC\_CAL и RTC\_PRL периодически происходит одновременное выполнение событий RTC\_DIV == RTC\_PRL и RTC\_20 == 0, которое приводит к ошибочному сбросу счетчика RTC\_DIV и пропуску импульса SEC\_CLK. При пропуске импульса SEC\_CLK основной счетчик RTC\_CNT не изменяется и начинает отставать на 1 секунду, при этом флаги SECF, ALRF и OWF в регистре RTC\_CS продолжают формироваться без пропусков.

#### **Условия**

Установлена калибровка частоты RTC\_CLK (поле RTC\_CAL[7:0] !=0) и заданы определенные значения RTC\_CAL и RTC\_PRL, при которых периодически происходит одновременное выполнение событий RTC\_DIV == RTC\_PRL и RTC\_20 ==0.

#### Последствия

Счетчик RTC\_DIV ошибочно сбрасывается, импульс SEC\_CLK не формируется. При пропуске импульса SEC\_CLK основной счетчик RTC\_CNT не изменяется и начинает отставать на 1 секунду, при этом флаги SECF, ALRF и OWF в регистре RTC\_CS продолжают формироваться без пропусков.

## Рекомендации и способы обхода

Для калибровки частоты RTC\_CLK использовать только ограниченный набор значений RTC\_CAL, полученный с помощью скрипта<sup>1</sup> для заданного значения RTC\_PRL. Перед настройкой блок RTC должен быть выключен и сброшен, при настройке регистр RTC\_DIV не должен изменяться. После настройки и включения RTC значения RTC\_CAL[7:0], RTC\_DIV и RTC\_PRL не должны перезаписываться. В этом случае ошибка проявляться не будет. Пример инициализации RTC:

- включить источник тактирования RTC и выбрать его в RTC\_SEL[1:0] регистра REG\_0F;

- выключить RTC путем сброса бита RTC\_EN в регистре REG\_0F;

- выдержать паузу не менее 1 периода RTC\_CLK для ожидания сброса бита RTC\_EN;

- выполнить сброс RTC путем последовательной установки и сброса бита RTC\_RESET в регистре REG\_0F;

- записать требуемое значение в регистр RTC\_PRL;

- дождаться окончания записи с помощью бита WEC в регистре RTC\_CS;

- записать допустимое значение в поле RTC\_CAL[7:0] регистра REG\_0F;

<sup>&</sup>lt;sup>1</sup> https://support.milandr.ru/upload/iblock/285/9bliqywbkpifcoptft5dctv327ycqh9s/bkp\_rtc\_cal.py

- выполнить другие настройки RTC;

- включить RTC путем установки бита RTC\_EN в регистре REG\_0F.

# Лист регистрации изменений

Дата документа: 22/10/25

| Дата     | Страница | Статус | ID   | Категория | Описание                                    |

|----------|----------|--------|------|-----------|---------------------------------------------|

| 28.04.22 |          |        |      |           | Документ создан                             |

| 14.06.22 | 25       |        | 0032 | 3         | Добавлено описание ошибки                   |

| 21.06.22 |          |        |      |           | Добавлено описание ошибок ревизии 4         |

| 07.12.22 | 24       |        | 0020 | 3         | Описание и статус ошибки скорректированы    |

| 07.06.23 | 30       |        | 0033 | 3         | Добавлено описание ошибки                   |

| 02.08.24 | 11       |        | 0025 | 2         | В описании исправлена пунктуационная ошибка |

|          | 24       |        | 0020 | 3         | Исправлено название ошибки;                 |

|          | 32       |        | 0034 | 3         | Добавлено описание ошибки;                  |

|          | 33       |        | 0035 | 3         | Добавлено описание ошибки                   |

| 27.03.25 | 21       |        | 0007 | 3         | Добавлено описание ошибки;                  |

|          | 34       |        | 0036 | 3         | Добавлено описание ошибки                   |

| 22.10.25 | 35       |        | 0037 | 3         | Добавлено описание ошибки                   |

|          |          |        |      |           |                                             |

|          |          |        |      |           |                                             |

|          |          |        |      |           |                                             |

|          |          |        |      |           |                                             |

|          |          |        |      |           |                                             |

|          |          |        |      |           |                                             |

|          |          |        |      |           |                                             |

|          |          |        |      |           |                                             |

|          |          |        |      |           |                                             |