# Микросхема 20-разрядного сигма-дельта АЦП с токовыми входами (8 каналов) 5101HB035, K5101HB035K

ГГ – год выпуска НН – неделя выпуска

## Основные характеристики микросхемы:

- Напряжение питания от 3,0 до 3,6 В;

- Шкала значений накопленного заряда от 12 до 350 пКл;

- Время интегрирования от 10 мкс до 1 с;

- Скорость преобразования от 1 до 2500 выб/с;

- Разрешающая способность 16/20 бит;

- Шкала измеряемых напряжений от 0 до 2,5 В или ± 2,5 В;

- Входной ток смещения по входам AIN1 – AIN8 <10 пА;</li>

- Динамический ток потребления до 2 мА/канал;

Рабочий диапазон температур:

| Обозначение | Диапазон         |

|-------------|------------------|

| 5101HB035   | минус 60 – 85 °C |

| K5101HB035  | минус 60 – 85 °C |

| K5101HB035K | 0 – 70 °C        |

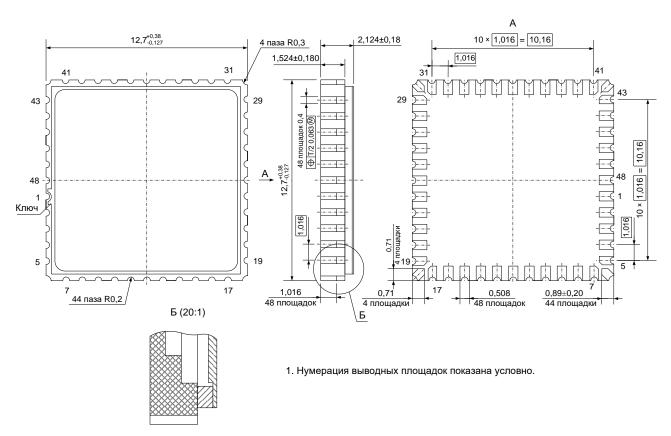

## Тип корпуса:

- 48-выводой металлокерамический корпус 5142.48-А.

## Общее описание и область применения микросхемы

Микросхемы интегральные 5101HB035, 20-разрядный сигма-дельта АЦП с токовыми входами (8 каналов), (далее – микросхемы) представляют собой готовое решение для высокоточных измерений токов малых значений в диапазоне от пико- до микроампер.

Микросхемы содержат:

- 16 интеграторов тока;

- таймер времени интегрирования;

- 8 сигма-дельта АЦП с эффективной разрешающей способностью до 20 бит;

- перестраиваемый цифровой фильтр с выходной частотой от 1 до 2500 Гц для токовых режимов и от 1 до 5300 Гц для режимов измерения напряжений;

- источник опорного напряжения (ИОН), используется в качестве шкалы АЦП (предусмотрена возможность работы от внешней опоры);

- внутренний RC-генератор (предусмотрена возможность работы от внешнего тактового генератора);

- интерфейс DCH;

- интерфейс SPI.

# Содержание

| 1  | Стр  | уктурная блок-схема микросхем                                          | . 3 |

|----|------|------------------------------------------------------------------------|-----|

| 2  | Усл  | овное графическое обозначение                                          | . 4 |

| 3  | Опи  | ісание выводов                                                         | . 5 |

| 4  | Указ | зания по применению и эксплуатации                                     | . 7 |

| 5  |      | ісание функционирования микросхемы                                     |     |

|    |      | Включение питания и инициализация                                      |     |

|    |      | Последовательный интерфейс SPI                                         |     |

|    | 5.3  | Описание регистров микросхемы                                          | 12  |

|    |      | 5.3.1 Регистр команд СОМ                                               | 12  |

|    |      | 5.3.2 Регистр состояния STAT                                           | 13  |

|    |      | 5.3.3 Регистр конфигурации CFG                                         | 13  |

|    |      | 5.3.4 Регистры данных DATA1-8                                          |     |

|    |      | 5.3.5 Регистр длительности интегрирования TINT                         | 16  |

|    | 5.4  | Режимы работы микросхемы                                               | 17  |

|    |      | 5.4.1 Режим преобразования тока с внешним управлением (MDS = 000)      | 17  |

|    |      | 5.4.2 Режим преобразования тока с внутренним управлением (MDS = 001) 2 | 23  |

|    |      | 5.4.3 Режим преобразования положительного напряжения (MDS=010)         | 24  |

|    |      | 5.4.4 Режим преобразования дифференциального напряжения (MDS=100):     | 24  |

|    |      | 5.4.5 Режим пониженного потребления (MDS=011)                          |     |

| 6  |      | овые схемы включения                                                   |     |

| 7  |      | овые зависимости                                                       |     |

| 8  |      | ктрические параметры микросхем                                         |     |

| 9  |      | дельно-допустимые и предельные параметры                               |     |

| 10 |      | авочные данные                                                         |     |

| 11 | Габа | аритный чертеж микросхемы                                              | 40  |

| 12 | Инф  | оормация для заказа 4                                                  | 41  |

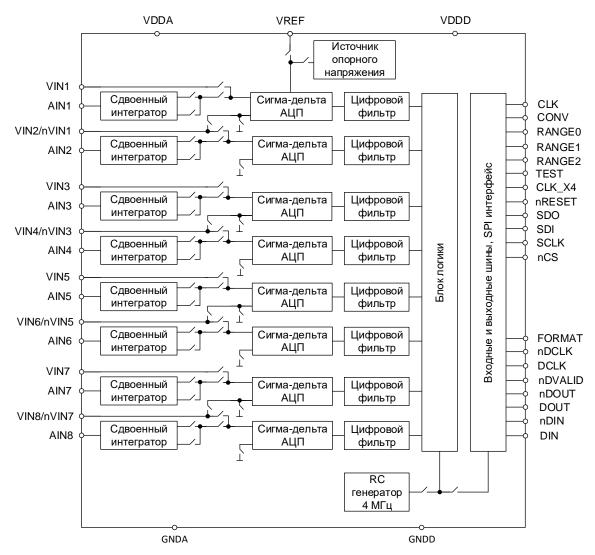

# 1 Структурная блок-схема микросхем

Функциональное назначение – 20-разрядный сигма-дельта АЦП с токовыми входами (8 каналов)

Рисунок 1 – Структурная блок-схема микросхем

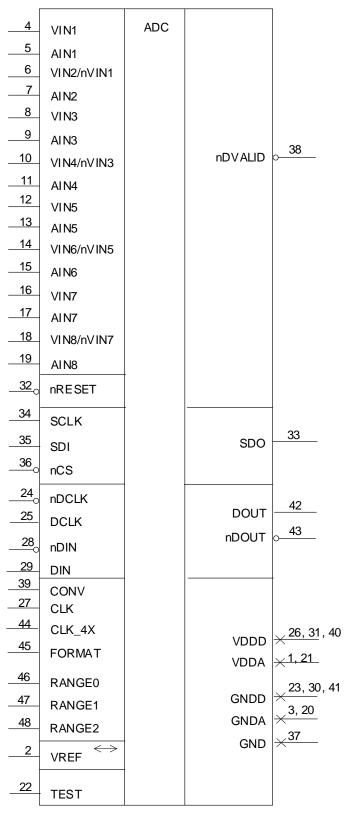

# 2 Условное графическое обозначение

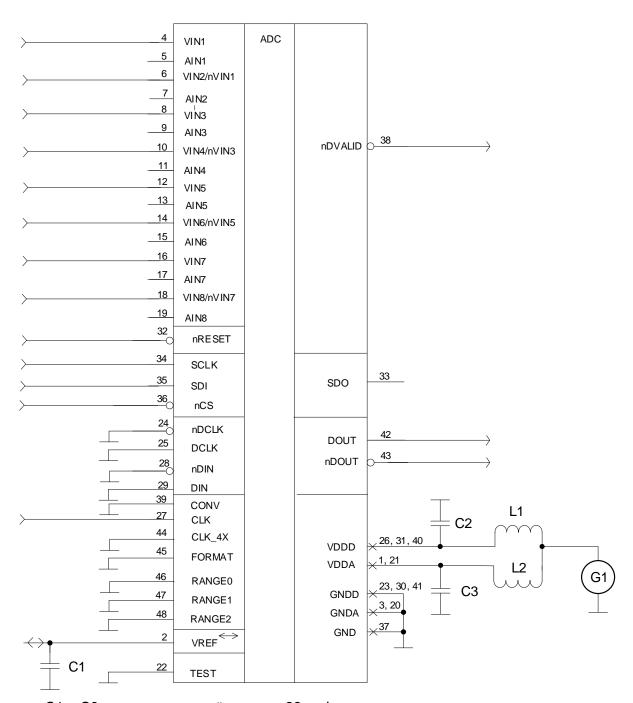

Рисунок 2 – Условное графическое обозначение микросхем

# 3 Описание выводов

Таблица 1 – Описание выводов

| №<br>выводной<br>площадки<br>корпуса | Обозначение<br>вывода | Тип<br>вывода | Функциональное назначение вывода                                                            |

|--------------------------------------|-----------------------|---------------|---------------------------------------------------------------------------------------------|

| 1                                    | VDDA                  | PWR           | Питание аналоговых блоков                                                                   |

| 2                                    | VREF                  | Ю             | Вход опорного напряжения 2,4 В/Выход внутреннего источника опорного напряжения              |

| 3                                    | GNDA                  | PWR           | Общий аналоговых блоков                                                                     |

| 4                                    | VIN1                  | Al            | Вход канала 1 прямой                                                                        |

| 5                                    | AIN1                  | Al            | Вход канала 1 токовый                                                                       |

| 6                                    | VIN2/nVIN1            | Al            | Вход канала 2/Вход канала 1 инверсный                                                       |

| 7                                    | AIN2                  | Al            | Вход канала 2 токовый                                                                       |

| 8                                    | VIN3                  | Al            | Вход канала 3 прямой                                                                        |

| 9                                    | AIN3                  | Al            | Вход канала 3 токовый                                                                       |

| 10                                   | VIN4/nVIN3            | Al            | Вход канала 4/Вход канала 3 инверсный                                                       |

| 11                                   | AIN4                  | Al            | Вход канала 4 токовый                                                                       |

| 12                                   | VIN5                  | Al            | Вход канала 5 прямой                                                                        |

| 13                                   | AIN5                  | ΑI            | Вход канала 5 токовый                                                                       |

| 14                                   | VIN6/nVIN5            | ΑI            | Вход канала 6/Вход канала 5 инверсный                                                       |

| 15                                   | AIN6                  | ΑI            | Вход канала 6 токовый                                                                       |

| 16                                   | VIN7                  | ΑI            | Вход канала 7 прямой                                                                        |

| 17                                   | AIN7                  | ΑI            | Вход канала 7 токовый                                                                       |

| 18                                   | VIN8/nVIN7            | Al            | Вход канала 8/Вход канала 7 инверсный                                                       |

| 19                                   | AIN8                  | Al            | Вход канала 8 токовый                                                                       |

| 20                                   | GNDA                  | PWR           | Общий аналоговых блоков                                                                     |

| 21                                   | VDDA                  | PWR           | Питание аналоговых блоков                                                                   |

| 22                                   | TEST                  | I             | Вход выбора тестового режима                                                                |

| 23                                   | GNDD                  | PWR           | Общий цифровых блоков                                                                       |

| 24                                   | nDCLK                 | 1             | Вход сигнала синхронизации последовательного интерфейса инверсный                           |

| 25                                   | DCLK                  | I             | Вход сигнала синхронизации последовательного интерфейса прямой                              |

| 26                                   | VDDD                  | PWR           | Питание цифровых блоков                                                                     |

| 27                                   | CLK                   | ı             | Вход сигнала внешней тактовой частоты АЦП                                                   |

| 28                                   | nDIN                  | I             | Вход данных последовательного интерфейса инверсный                                          |

| 29                                   | DIN                   | I             | Вход данных последовательного интерфейса прямой                                             |

| 30                                   | GNDD                  | PWR           | Общий цифровых блоков                                                                       |

| 31                                   | VDDD                  | PWR           | Питание цифровых блоков                                                                     |

| 32                                   | nRESET                |               | Вход сброса микросхемы                                                                      |

| 33                                   | SDO                   | 0             | Выход данных интерфейса SPI                                                                 |

| 34                                   | SCLK                  |               | Вход сигнала синхронизации интерфейса SPI                                                   |

| 35                                   | SDI                   |               | Вход данных интерфейса SPI                                                                  |

| 36                                   | nCS                   |               | Вход выбора ведомого устройства интерфейса SPI                                              |

| 37                                   | GND                   | PWR           | Общий площадок ввода-вывода. Электрически соединён с металлизацией обратной стороны корпуса |

| 38                                   | nDVALID               | 0             | Выход сигнала готовности данных                                                             |

| 39                                   | CONV                  |               | Вход сигнала управления временем интегрирования                                             |

| 40                                   | VDDD                  | PWR           | Питание цифровых блоков                                                                     |

| 41                                   | GNDD                  | PWR           | Общий цифровых блоков                                                                       |

| 42                                   | DOUT                  | 0             | Выход сигнала данных последовательного интерфейса прямой                                    |

| №<br>выводной<br>площадки<br>корпуса | Обозначение<br>вывода | Тип<br>вывода | Функциональное назначение вывода                                      |

|--------------------------------------|-----------------------|---------------|-----------------------------------------------------------------------|

| 43                                   | nDOUT                 | 0             | Выход сигнала данных последовательного интерфейса инверсный           |

| 44                                   | CLK_4X                | I             | Вход сигнала выбора коэффициента деления внешней тактовой частоты АЦП |

| 45                                   | FORMAT                | I             | Вход конфигурации разрядности выходных данных АЦП                     |

| 46                                   | RANGE0                | I             | Вход выбора полной шкалы интегратора                                  |

| 47                                   | RANGE1                | I             | Вход выбора полной шкалы интегратора                                  |

| 48                                   | RANGE2                | I             | Вход выбора полной шкалы интегратора                                  |

Примечание – Обозначение типов выводов:

– аналоговый вход;

П — цифровой вход;

О — цифровой выход;

ІО — цифровой вход/выход;

РWR — вывод «Питание» и «Общий»

## 4 Указания по применению и эксплуатации

При ремонте аппаратуры и измерении параметров замену микросхем необходимо проводить только при отключенных источниках питания.

Типовые схемы включения микросхем приведены на рисунках 16, 17.

Вывод TEST необходимо подключать к шине «Общий».

Неиспользуемые цифровые входы должны быть доопределены до допустимых логических уровней напряжения.

Неиспользуемые аналоговые входы VIN1 – VIN8 рекомендуется подключать к шине «Общий», неиспользуемые аналоговые входы AIN1 – AIN8 – оставлять неподключенными.

Порядок подачи и снятия напряжения питания и входных сигналов на микросхемы следующий:

- подача (включение микросхем) «Общий», «Питание», входные сигналы или одновременно;

- снятие (выключение микросхем) в обратном порядке или одновременно.

## 5 Описание функционирования микросхемы

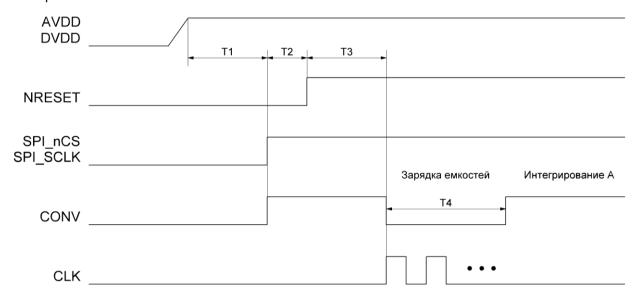

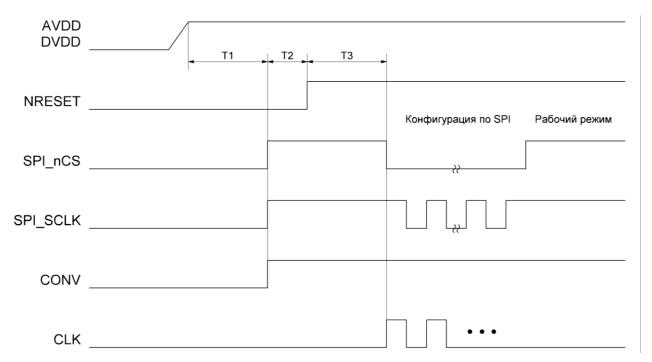

#### 5.1 Включение питания и инициализация

Перед включением питания все цифровые и аналоговые входы должны иметь низкий уровень. После стабилизации напряжения питания на вход nRESET подается высокий уровень (с задержкой T1). Далее на вход CLK подается сигнал тактовой частоты, а на вход CONV – сигнал, который формирует временную диаграмму управления АЦП (с задержкой T2).

Для того, чтобы в процессе функционирования перевести АЦП в начальное состояние, необходимо подать на вход nRESET низкий уровень длительностью не менее 50 мкс. По завершении указанного времени на вход nRESET подается высокий уровень, при этом АЦП переходит в то же состояние, что и при включении питания. Далее на вход CLK подается сигнал тактовой частоты, а на вход CONV — сигнал, который формирует временную диаграмму управления АЦП (с задержкой T2).

Диаграмма включения питания показана на рисунке 3. Значения временных параметров при включении питания и повторной инициализации АЦП приведены в таблице 2.

Рисунок 3 – Диаграмма включения питания в режим MDS=000 без использования SPI

Рисунок 4 – Диаграмма чтения данных при использовании одного АЦП Таблица 2 – Временные параметры при включении питания и инициализации

| Наименование параметра,                       | Буквенное<br>обозначение | Значение параметра |          |  |

|-----------------------------------------------|--------------------------|--------------------|----------|--|

| единица измерения                             | параметра                | не менее           | не более |  |

| Время задержки установки начального состояния |                          |                    |          |  |

| входных сигналов относительно момента         | T1                       | 10                 | -        |  |

| стабилизации напряжения питания, мс           |                          |                    |          |  |

| Время задержки положительного фронта сигнала  |                          |                    |          |  |

| NRESET относительно момента установки         | T2                       | 1                  | -        |  |

| начального состояния входных сигналов, мкс    |                          |                    |          |  |

| Время задержки переключений сигналов CONV,    |                          |                    |          |  |

| CLK, SPI_nCS и SPI_SCLK относительно          | T3                       | 1                  | -        |  |

| положительного фронта сигнала NRESET, мс      |                          |                    |          |  |

| Длительность первого импульса сигнала CONV,   | Τ.4                      | 50                 |          |  |

| MKC                                           | T4                       | 50                 | -        |  |

| Длительность низкого уровня сигнала NRESET    | TE                       | F0                 |          |  |

| при повторной инициализации, мкс              | T5                       | 50                 | -        |  |

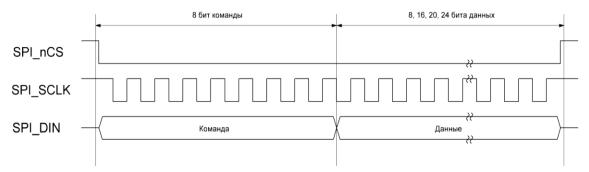

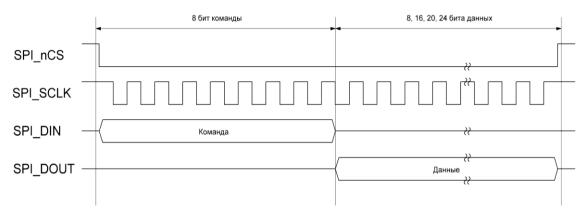

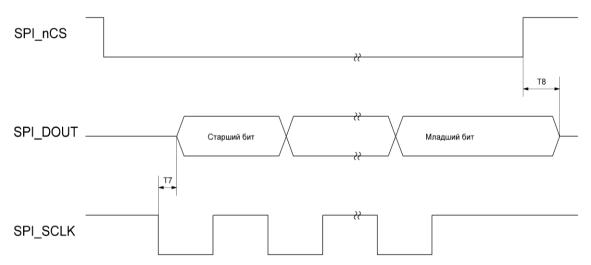

#### 5.2 Последовательный интерфейс SPI

Взаимодействия с АЦП по шине SPI осуществляются транзакциями при низком уровне сигнала SPI\_nCS. При высоком уровне сигнала SPI\_nCS контроллер SPI находится в исходном состоянии, вывод SPI\_DOUT находится в состоянии высокого импеданса. В исходном состоянии сигнал синхронизации SPI\_SCLK должен иметь высокий уровень, передача данных производится по отрицательному фронту сигнала SPI\_SCLK, прием данных производится по положительному фронту сигнала SPI\_SCLK.

Все взаимодействия с АЦП начинаются с операции записи в регистр команд. Регистр команд является 8-разрядным регистром, который доступен только для записи. Данные, записанные в регистр команд, определяют тип следующей операции (запись или чтение) и адрес регистра, к которому относится следующая операция. После завершения записи в указанный регистр или чтения из указанного регистра контроллер SPI возвращается в исходное состояние, при котором он ожидает следующую запись в регистр команд.

Диаграммы записи и чтения данных по шине SPI показаны на рисунках 5 и 6.

Рисунок 5 – Диаграмма записи данных в регистр по шине SPI

Рисунок 6 – Диаграмма чтения данных из регистра по шине SPI

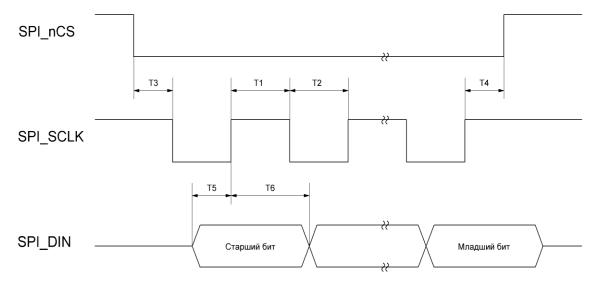

Временные диаграммы записи и чтения данных по шине SPI показаны на рисунках 7 и 8. Значения временных параметров приведены в таблице 3.

Рисунок 7 – Временная диаграмма записи данных в регистр по шине SPI

Рисунок 8 – Временная диаграмма чтения данных из регистра по шине SPI Таблица 3 – Временные параметры при записи и чтении данных по шине SPI

| Нешенополиче порометь                                                                                                 | Буквенное   | Значение параметра |          |  |

|-----------------------------------------------------------------------------------------------------------------------|-------------|--------------------|----------|--|

| Наименование параметра                                                                                                | обозначение | не менее           | не более |  |

| Длительность высокого уровня сигнала SPI_SCLK, нс                                                                     | T1          | 30                 |          |  |

| Длительность низкого уровня сигнала SPI_SCLK, нс                                                                      | T2          | 30                 |          |  |

| Время установки сигнала SPI_nCS относительно отрицательного фронта сигнала SPI_SCLK, нс                               | Т3          | 20                 |          |  |

| Время удержания сигнала SPI_nCS относительно положительного фронта сигнала SPI_SCLK, нс                               | T4          | 20                 |          |  |

| Время установки данных относительно положительного фронта сигнала SPI_SCLK, нс                                        | T5          | 10                 |          |  |

| Время удержания данных относительно положительного фронта сигнала SPI_SCLK, нс                                        | T6          | 10                 |          |  |

| Время задержки данных относительно<br>отрицательного фронта сигнала SPI_SCLK, нс                                      | T7          | 0                  | 20       |  |

| Время перехода сигнала SPI_DOUT в состояние высокого импеданса относительно положительного фронта сигнала SPI_nCS, нс | T8          | 0                  | 20       |  |

#### 5.3 Описание регистров микросхемы

Микросхема содержит набор встроенных регистров, которые используются для управления, настройки и тестирования устройства. Список регистров приведен в таблице 4.

Таблица 4 – Встроенные регистры микросхемы

| Адрес | Назв. | Биты    | Бит 7 | Бит 6    | Бит 5 | Бит 4       | Бит 3   | Бит 2   | Бит 1   | Бит 0 | Сброс    |

|-------|-------|---------|-------|----------|-------|-------------|---------|---------|---------|-------|----------|

| 0x0   | СОМ   | [7:0]   | WEN   | RNW      |       | RA[3:0] 0 0 |         |         | 0x00    |       |          |

| 0x0   | STAT  | [7:0]   | RDY   | 0        | 0     | 0           | 0       | 0       | 0       | INIT  | 0x81     |

|       |       | [23:16] | R.A   | NGE[2:   | 0]    | FRMT        | CLK4    | CONV    | REFS    | CLKS  |          |

| 0x1   | CFG   | [15:8]  | N     | 1DS[2:0] |       | TEST        |         | FS      | [3:0]   |       | 0x000000 |

|       |       | [7:0]   |       |          |       | СНІ         | D[7:0]  |         |         |       |          |

| 0x2   | DAT1  | [19:0]  |       | DATA1    |       |             |         | 0x00000 |         |       |          |

| 0x3   | DAT2  | [19:0]  |       | DATA2    |       |             |         | 0x00000 |         |       |          |

| 0x4   | DAT3  | [19:0]  |       |          |       | DA          | TA3     |         |         |       | 0x00000  |

| 0x5   | DAT4  | [19:0]  |       | DATA4    |       |             |         | 0x00000 |         |       |          |

| 0x6   | DAT5  | [19:0]  |       | DATA5    |       |             |         | 0x00000 |         |       |          |

| 0x7   | DAT6  | [19:0]  |       | DATA6    |       |             |         |         | 0x00000 |       |          |

| 0x8   | DAT7  | [19:0]  | DATA7 |          |       |             |         | 0x00000 |         |       |          |

| 0x9   | DAT8  | [19:0]  | DATA8 |          |       |             | 0x00000 |         |         |       |          |

| 0xA   | TINT  | [23:0]  |       |          |       | Т           | INT     |         |         |       | 0x000000 |

Примечания

Регистр СОМ доступен только для записи.

2 Регистры STAT, DAT1 – DAT8 доступны только для чтения

#### 5.3.1 Регистр команд СОМ

Регистр команд является 8-разрядным регистром, который доступен только для записи. Все взаимодействия с АЦП должны начинаться с операции записи в регистр команд. Данные, записанные в регистр команд, определяют тип следующей операции (запись или чтение) и адрес регистра, к которому относится следующая операция. После завершения записи в указанный регистр или чтения из указанного регистра контроллер SPI возвращается в исходное состояние, при котором он ожидает следующую запись в регистр команд.

Назначение битов регистра команд приведено в таблице 5, адрес регистра равен 0x0, значение при инициализации АЦП равно 0x00.

Таблица 5 – Биты регистра взаимодействия СОМ

| <b>№</b><br>битов | Название | Назначение                                                                                                                                                                                                                                                                                                                             |

|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                 | WEN      | Разрешение записи в регистр команд:  0 – запись в регистр команд разрешена;  1 – запись в регистр команд запрещена.  Пока первый бит команды равен 1, контроллер SPI не формирует сигнала синхронизации для записи последующих битов команды. Когда первый бит команды станет равен 0, следующие 7 бит будут записаны в регистр команд |

| <b>№</b><br>битов | Название | Назначение                                                                                            |

|-------------------|----------|-------------------------------------------------------------------------------------------------------|

| 6                 | RNW      | Тип операции с выбранным регистром: 0 – запись в выбранный регистр; 1 – чтение из выбранного регистра |

| 52                | RA[3:0]  | Адрес выбранного регистра                                                                             |

| 1                 | ı        | Должен быть всегда равен 0 для правильного функционирования                                           |

| 0                 | -        | Должен быть всегда равен 0 для правильного функционирования                                           |

#### 5.3.2 Регистр состояния STAT

Регистр состояния является 8-разрядным регистром, который доступен только для чтения. Назначение битов регистра приведено в таблице 6, адрес регистра равен 0x0, значение при инициализации АЦП равно 0x81.

Таблица 6 – Биты регистра состояния STAT

| №<br>битов | Название | Назначение                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7          | RDY      | Бит готовности данных. Значение бита становится равным 0, когда результаты преобразования записываются в регистры данных. Значение бита становится равным 1 после чтения любого регистра данных. При записи результатов преобразования в регистры данных на выходе SPI_DOUT формируется низкий уровень. Контроль состояния данного выхода является альтернативой постоянному чтению регистра состояния |  |  |  |  |

| 61         | 1        | Данные биты всегда равны 0                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 0          | INIT     | Бит индикации инициализации. Значение бита равно 1 во время процедуры инициализации микросхемы. До ее завершения не следует производить никаких действий с микросхемой, кроме чтения регистра состояния. Подробнее см. раздел «Включение питания и инициализация»                                                                                                                                      |  |  |  |  |

## 5.3.3 Регистр конфигурации CFG

Регистр конфигурации является 24-разрядным регистром, который доступен для записи и чтения. Назначение битов регистра приведено в таблице 7, адрес регистра равен 0x1, значение при инициализации АЦП равно 0x000000.

Таблица 7 – Биты регистра конфигурации CFG

| №<br>битов Название Назначение                                                                                                                                                                                                                                                                                                |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Выбор шкалы интегрирования* в режиме MDS = 001:  000 – полная шкала равна 12 пКл; 001 – полная шкала равна 50 пКл; 010 – полная шкала равна 100 пКл; 011 – полная шкала равна 150 пКл; 100 – полная шкала равна 200 пКл; 101 – полная шкала равна 250 пКл; 110 – полная шкала равна 300 пКл; 111 – полная шкала равна 350 пКл |  |

| <b>№</b><br>битов | Название | Назначение                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 505               |          | Выбор формата (разрядности) выходных данных:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20                | FRMT     | 0 – 16 бит;<br>1 – 20 бит.<br>В режиме MDS = 000 управление разрядностью выходных данных осуществляется внешним входом FORMAT с аналогичной таблицей истинности                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19                | CLK4     | Управление делителем тактовой частоты во всех режимах, кроме режима MDS = 000:  0 – деление тактовой частоты на 1;  1 – деление тактовой частоты на 4.  В режиме MDS = 000 управление делителем тактовой частоты осуществляется внешним входом CLK_4X с аналогичной таблицей истинности                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18                | CONV     | Выбор первого интегратора (А или В) в режиме MDS= 001:  0 – первым работает интегратор А;  1 – первым работает интегратор В.  В режиме MDS = 000 управление интеграторами осуществляется внешним входом CONV. Подробнее см. рисунки 9, 10, 11                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17                | REFS     | Выбор источника опорного напряжения 2,4 В:  0 – внешний источник опорного напряжения 2,4 В;  1 – внутренний источник опорного напряжения 2,4 В                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16                | CLKS     | Выбор источника тактового сигнала:  0 – внешний источник 4 МГц (при CLK4 = 0) или 16 МГц (при CLK4 = 1);  1 – внутренний RC-генератор 4 МГц (значение CLK4 не влияет)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1513              | MDS[2:0] | Выбор режима функционирования:  000 — режим преобразования тока на входах AIN1, AIN2, AIN3, AIN4, AIN5, AIN6, AIN7, AIN8. Управление режимом осуществляется внешними выводами микросхемы;  001 — режим преобразования тока на входах AIN1, AIN2, AIN3, AIN4, AIN5, AIN6, AIN7, AIN8. Управление режимом осуществляется через SPI;  010 — режим преобразования положительного напряжения на входах VIN1, VIN2, VIN3, VIN4, VIN5, VIN6, VIN7, VIN8. Управление режимом осуществляется через SPI;  011 — режим «выключено». Минимальное потребление;  100 — режим преобразования дифференциального напряжения на входах VIN1-2; VIN3-4; VIN5-6; VIN7-8. Управление режимом осуществляется через SPI |

| 12                | TEST     | Должен быть всегда равен 0 для правильного функционирования                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 118               | FS[3:0]  | Выбор коэффициента децимации цифрового фильтра, подробнее в таблице 14 (измерение токов) и в таблице 16 (измерение напряжений)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| №<br>битов | Название                | Назначение                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70         | CHD[7:0]                | Выборочное включение/отключение аналоговых каналов:  CHD[0] = 0/1 канал №1 включен/отключен;  CHD[1] = 0/1 канал №2 включен/отключен;  CHD[2] = 0/1 канал №3 включен/отключен;  CHD[3] = 0/1 канал №4 включен/отключен;  CHD[4] = 0/1 канал №5 включен/отключен;  CHD[5] = 0/1 канал №6 включен/отключен;  CHD[6] = 0/1 канал №7 включен/отключен;  CHD[7] = 0/1 канал №8 включен/отключен. |

|            | * Значение на           | опленного заряда Q определяется по формуле                                                                                                                                                                                                                                                                                                                                                  |

|            |                         | $Q = I_{INP} \cdot t_{INT,} \tag{1}$                                                                                                                                                                                                                                                                                                                                                        |

|            | где                     | Y AINIA AINIO                                                                                                                                                                                                                                                                                                                                                                               |

|            |                         | ой ток по входам AIN1 – AIN8;                                                                                                                                                                                                                                                                                                                                                               |

|            | t <sub>імт</sub> — врем | интегрирования, определяемое регистром TINT (см. таблицу 10)                                                                                                                                                                                                                                                                                                                                |

#### 5.3.4 Регистры данных DATA1-8

Регистры данных являются 20-разрядными регистрами, которые доступны только для чтения. Каждый регистр данных содержит результат преобразования соответствующего канала АЦП (регистр DAT1 содержит результат преобразования канала №1, регистр DAT2 содержит результат преобразования канала №2 и т.д.). Назначение регистров приведено в таблице 8, адреса регистров равны 0х2 – 0х9, значения при инициализации равны 0х00000.

Если значение бита FRMT равно 1, то при чтении данных выдаются все 20 бит результата. Если значение бита FRMT равно 0, то при чтении данных выдаются старшие 16 бит результата.

Таблица 8 – Биты регистров данных DAT1 – DAT8

| №<br>битов | Название   | Назначение                         |

|------------|------------|------------------------------------|

|            | DAT1[19:0] | Результат преобразования канала №1 |

|            | DAT2[19:0] | Результат преобразования канала №2 |

|            | DAT3[19:0] | Результат преобразования канала №3 |

| 190        | DAT4[19:0] | Результат преобразования канала №4 |

| 190        | DAT5[19:0] | Результат преобразования канала №5 |

|            | DAT6[19:0] | Результат преобразования канала №6 |

|            | DAT7[19:0] | Результат преобразования канала №7 |

|            | DAT8[19:0] | Результат преобразования канала №8 |

Таблица 9 – Кодирование результата в режимах преобразования тока

| Входной<br>сигнал,<br>% шкалы | Пример для<br>RANGE = 111,<br>пКл | Результат<br>преобразования<br>при FORMAT = 1 | Результат<br>преобразования<br>при FORMAT = 0 |

|-------------------------------|-----------------------------------|-----------------------------------------------|-----------------------------------------------|

| 100                           | 350                               | 0xFFFFF                                       | 0xFFFF                                        |

| 0                             | 0                                 | 0x01000                                       | 0x0100                                        |

| -0,3955                       | -1,3843                           | 0x00000                                       | 0x0000                                        |

Кодирование результатов преобразования АЦП зависит от текущего режима функционирования. В режимах преобразования тока (MDS = 000 или MDS = 001) результат преобразования представляет собой двоичное смещение относительно уровня -0,3955 % FS, как показано в таблице 9.

В режиме преобразования положительного напряжения (MDS = 010) результат преобразования представляет собой двоичное смещение относительно нуля. Например, при нулевом сигнале результат преобразования равен 0x00000, при максимальном положительном сигнале результат преобразования равен 0xFFFFF. Результат преобразования при таком кодировании выражается следующими формулами

DATA =

$$2^{20} \cdot VIN / VREF$$

(при FORMAT = 1), (2)

DATA =

$$2^{16} \cdot VIN / VREF(\pi pu FORMAT = 0)$$

. (3)

В режиме преобразования дифференциального (MDS = 100) напряжения результат преобразования представляет собой двоичное смещение относительно отрицательного сигнала максимальной амплитуды. Например, при максимальном отрицательном дифференциальном сигнале результат преобразования равен 0x00000, при нулевом дифференциальном сигнале результат преобразования равен 0x80000, при максимальном дифференциальном положительном сигнале результат преобразования равен 0xFFFFF. Результат преобразования при таком кодировании выражается следующими формулами

DATA =

$$2^{19} + 2^{20} \cdot VIN_{dif} / (2 \cdot VREF)$$

(при FORMAT = 1), (4)

DATA =

$$2^{15} + 2^{16} \cdot VIN_{dif} / (2 \cdot VREF)$$

(при FORMAT = 0). (5)

#### 5.3.5 Регистр длительности интегрирования TINT

Регистр длительности интегрирования является 24-разрядным регистром, который доступен по записи и по чтению. Назначение битов регистра приведено в таблице 10, адрес регистра равен 0хA, значение при инициализации АЦП равно 0х000000.

Таблица 10 – Биты регистра длительности интегрирования

| №<br>битов | итов название назначение |                                                         |

|------------|--------------------------|---------------------------------------------------------|

| 230        | TINT[23:0]               | Длительность интегрирования в периодах тактовой частоты |

Таблица 11 – Управление временем интегрирования

| CLC_4X | CLKS | MDS | Частота<br>внешнего<br>генератора,<br>МГц | Допустимая<br>длительность<br>интегрирования | Шаг настройки<br>времени<br>интегрирования | Возможная ошибка времени интегрирования |

|--------|------|-----|-------------------------------------------|----------------------------------------------|--------------------------------------------|-----------------------------------------|

| 0      | 0    | 001 | 4                                         | 40 – 40000000                                | 1/F <sub>CLK</sub> = 250 нс                | 0                                       |

|        |      |     |                                           | тактов F <sub>CLK</sub>                      |                                            |                                         |

| 1      | 0    | 001 | 16                                        | 160-160000000                                | $1/F_{CLK} = 62,5 \text{ HC}$              | 0                                       |

|        |      |     |                                           | тактов F <sub>CLK</sub>                      |                                            |                                         |

| X      | 1    | 001 | -                                         | 40 – 40000000                                | 1/ F <sub>RCOSC</sub> ~ 250 нс             | до ±4 %                                 |

|        |      |     |                                           | тактов F <sub>RCOSC</sub>                    |                                            |                                         |

| 0      | 0    | 000 | 4                                         | 10 мкс – 1 сек                               | 1/F <sub>CLK</sub> = 250 HC                | до 250 нс                               |

| 1      | 0    | 000 | 16                                        | 10 мкс – 1 сек                               | $1/F_{CLK} = 62,5 \text{ HC}$              | до 62.5 нс                              |

| Х      | 1    | 000 | -                                         | 10 мкс – 1 сек                               | 1/ F <sub>RCOSC</sub> ~ 250 HC             | до ∼250 нс                              |

350

#### 5.4 Режимы работы микросхемы

#### 5.4.1 Режим преобразования тока с внешним управлением (MDS = 000)

Этот режим выбирается микросхемой по умолчанию при «сбросе». В нем микросхема измеряет втекающие токи на входах AIN1-8 путем накопления зарядов на интеграторах и последующей оцифровке накопленного значения с помощью сигмадельта АЦП.

В данном режиме функционирования интерфейс SPI можно не использовать. Т.к. сигналами управления микросхемы являются внешние выводы.

Bходы RANGE1, RANGE0 определяют шкалу интегрирования (см. таблицу 12).

| RANGE2 | RANGE1 | RANGE0 | Шкала интегрирования, пКл |

|--------|--------|--------|---------------------------|

| 0      | 0      | 0      | 12                        |

| 0      | 0      | 1      | 50                        |

| 0      | 1      | 0      | 100                       |

| 0      | 1      | 1      | 150                       |

| 1      | 0      | 0      | 200                       |

| 1      | 0      | 1      | 250                       |

| 1      | 1      | 0      | 200                       |

Таблица 12 – Выбор шкалы интегрирования

Вход CLK\_4X определяет коэффициент деления входной тактовой частоты (см. таблицу 13).

| CLK_4X | Коэффициент<br>деления<br>частоты | Входная<br>тактовая<br>частота,<br>МГц | Внутренняя<br>тактовая<br>частота,<br>МГц | Дискретность времени<br>интегрирования |

|--------|-----------------------------------|----------------------------------------|-------------------------------------------|----------------------------------------|

| 0      | 1                                 | 4                                      | 4                                         | 1/F <sub>CLK</sub> = 250 нсек          |

| 1      | 4                                 | 16                                     | 4                                         | 1/F <sub>CLK</sub> = 62,5 нсек         |

Таблица 13 – Выбор коэффициента деления тактовой частоты

Вход FORMAT определяет разрядность результатов преобразования АЦП. Если FORMAT = 1, то разрядность выходных данных АЦП равна 20 бит.

Если FORMAT = 0, то разрядность выходных данных АЦП равна 16 бит.

Вход CONV определяет время начала и продолжительность интегрирования входного тока на всех каналах AIN1-8 одновременно, а также управляет общей логикой функционирования микросхемы. Подробнее смотрите подраздел «Автомат управления в режиме интегрирования токов».

Выводы DCLK, nDCLK, DIN, nDIN, DOUT, nDOUT, nDVALID используются для передачи выходных данных АЦП по интерфейсу DCH.

Сигналы управления RANGE0-2 CLK\_4X, CONV, FORMAT синхронизируются по отрицательному фронту сигнала внешней тактовой частоты CLK.

Значения битов SPI: RANGE2, RANGE1, RANGE0, CLK4, CONV, FORMAT, TINT игнорируются. Тем не менее, все регистры SPI читаются и записываются точно также, как в любом другом режиме. Интерфейс SPI в режиме MDS = 000 можно использовать для конфигурации микросхемы посредством записи в биты REFS, CLKS, FS[3:0], CHD[7:0]. Конфигурацию следует записывать после подачи сигнала низкого уровня входного сигнала NRESET, и до начала работы. Подробнее см. рисунок 4.

SPI также можно использовать для считывания результатов преобразования АЦП из регистров DATA и переключения в другие режимы посредством записи

битов MDS[2:0]. При этом любая запись в регистр CFG будет сбрасывать автомат управления в состояние 0 или 4 (см. рисунок 9) аналогично подаче низкого уровня входного сигнала NRESET.

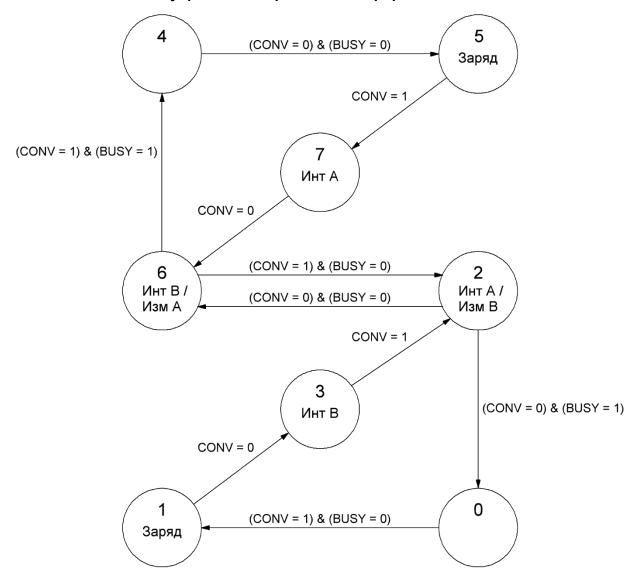

#### 5.4.1.1 Автомат управления в режиме интегрирования токов

Рисунок 9 – Диаграмма состояний автомата управления в режимах MDS=000/001

Управление интегрированием и преобразованием входного аналогового сигнала выполняется автоматом с конечным числом состояний, который показан на рисунке 9. Состояние автомата определяется значением сигнала CONV и значением внутреннего сигнала BUSY, который устанавливается аппаратным способом при выполнении преобразования.

Начальное состояние автомата определяется состоянием входного сигнала CONV, которое фиксируется во время низкого уровня входного сигнала NRESET:

- начальное состояние сигнала CONV равно 1 и начальное состояние автомата равно 4, если во время низкого уровня входного сигнала NRESET входной сигнал CONV имеет высокий уровень;

- начальное состояние сигнала CONV равно 0 и начальное состояние автомата равно 0, если во время низкого уровня входного сигнала NRESET входной сигнал CONV имеет низкий уровень.

В зависимости от сигнала CONV и значения конфигурационных бит FS[3:0] логика автомата осуществляет работу в двух возможных режимах:

- постоянное интегрирование входного сигнала;

- периодическое интегрирование входного сигнала.

Условие режима постоянного интегрирования – продолжительность высокого/низкого уровня сигнала CONV больше времени полного цикла преобразования (Т2 в таблице 14)

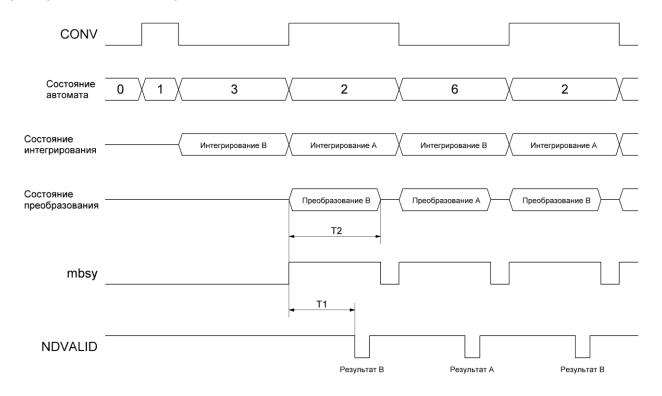

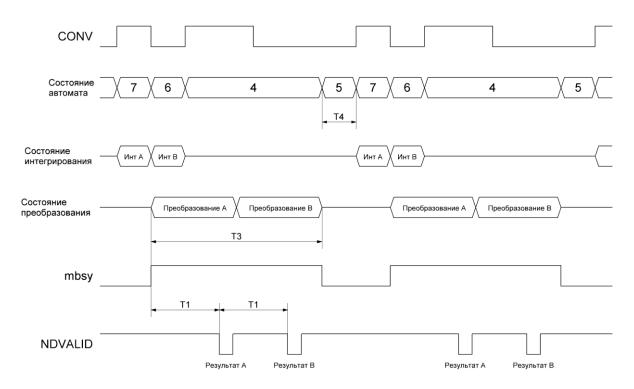

Диаграмма работы микросхемы в режиме постоянного интегрирования токов на входах AIN1-8 показана на рисунке 10, диаграмма в режиме периодического интегрирования показана на рисунке 11. Значения временных параметров в режиме преобразования тока приведены в таблице 14.

Рисунок 10 – Диаграмма функционирования микросхемы в режиме постоянного интегрирования

Рисунок 11 — Диаграмма функционирования микросхемы в режиме периодического интегрирования

Таблица 14 – Временные параметры в режимах преобразования тока

| Значение | Время готовности | Время полного цикла    | Частота        |

|----------|------------------|------------------------|----------------|

| FS       | данных Т1, мкс   | преобразования Т2, мкс | преобразования |

| 0000     | 379,5            | 397,5                  | 2,51 КГц       |

| 0001     | 427,5            | 445,5                  | 2,24 КГц       |

| 0010     | 619,5            | 637,5                  | 1,56 КГц       |

| 0011     | 811,5            | 829,5                  | 1,2 КГц        |

| 0100     | 1003,5           | 1021,5                 | 978,9 Гц       |

| 0101     | 2005             | 2023                   | 494,3 Гц       |

| 0110     | 3925             | 3943                   | 253,6 Гц       |

| 0111     | 15445            | 15463                  | 64,6 Гц        |

| 1000     | 30805            | 30823                  | 32,4 Гц        |

| 1001     | 61525            | 61543                  | 16,2 Гц        |

| 1010     | 122965           | 122983                 | 8,1 Гц         |

| 1011     | 307285           | 307303                 | 3,2 Гц         |

| 1100     | 614485           | 614503                 | 1,6 Гц         |

| 1101     | 983125           | 983143                 | 1,01 Гц        |

| 1110     | 1966248          | 1966266                | 0,50 Гц        |

| 1111     | 3932328          | 3932346                | 0,25 Гц        |

Примечание — Время готовности данных и время полного цикла преобразования приведены при внешней тактовой частоте 4 МГц

В режиме периодического интегрирования время преобразования Т3 равно сумме времени готовности данных Т1 и времени преобразования Т2. Кроме того, в режиме периодического интегрирования пользователь должен управлять внешним сигналом CONV таким образом, чтобы время подготовки к интегрированию Т4 было больше 19 мкс.

По окончании преобразования формируется выходной сигнал NDVALID. Чтение результатов преобразования производится по интерфейсу DCH.

#### 5.4.1.2 Интерфейс DCH

Интерфейс DCH осуществляет синхронный последовательный сбор данных из одной или нескольких микросхем по цепочке. Он функционирует только при MDS = 000, когда микросхема управляется внешними выводами. Интерфейс DCH позволяет объединить в цепочку от 1-ой до 48-ми микросхем и получить из микросхем всю информацию, содержащуюся в регистрах DATA на данный момент без использования интерфейса SPI.

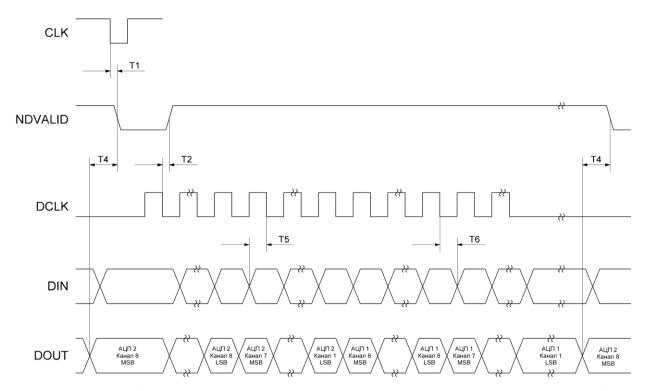

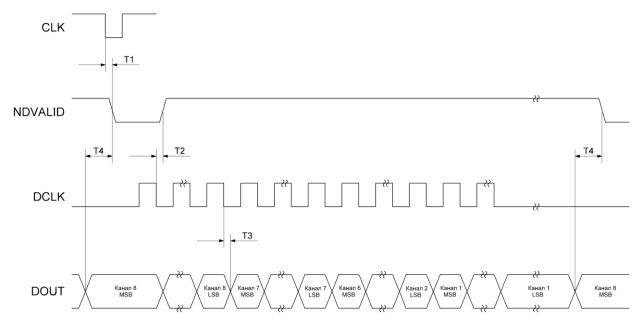

Для его работы необходим дифференциальный сигнал синхронизации данных (входы DCLK и nDCLK). Передача данных производится по отрицательному фронту сигнала DCLK. Сбор данных из цепочки микросхем следует начинать только после появления низкого уровня на выходе nDVALID. Переход NDVALID из 1 в 0 указывает, что преобразование АЦП завершено и данные готовы. Обратный переход происходит по первому срезу сигнала DCLK.

Диаграммы чтения данных по интерфейсу DCH показаны на рисунках 13 и 14. Значения временных параметров приведены в таблице 15.

Для уменьшения шума рекомендуется не передавать данные при изменении сигнала CONV. Следует приостанавливать изменение сигнала DCLK по крайней мере в течение 8 мкс до изменения сигнала CONV и в течение 8 мкс после изменения сигнала CONV.

Частота сигнала синхронизации интерфейса DCH, равная F<sub>DCLK</sub>, не зависит явным образом от частоты основного сигнала синхронизации всей микросхемы, равной F<sub>CLK</sub>. Максимально допустимое значение частоты F<sub>DCLK</sub> определено в технических условиях АЕНВ.431320.584ТУ (параметр f<sub>C</sub>). Минимально необходимое значение частоты F<sub>DCLK</sub> можно рассчитать по формуле

20 M

$$\Gamma$$

$\mu$   $\geq$  FDCLK  $\geq$  (NB/20)  $\cdot$  (Mc/48)  $\cdot$  20 M $\Gamma$  $\mu$ , (6)

где:

M<sub>C</sub> – количество микросхем, объединенных в цепь (от 1 до 48);

N<sub>в</sub> – разрядность выходных данных АЦП (16 или 20 бит).

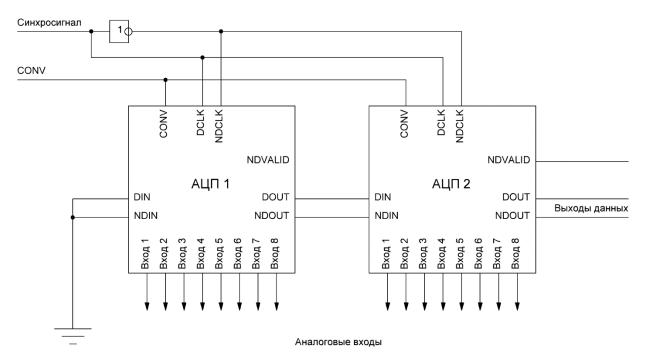

Для объединения нескольких микросхем в цепочку необходимо подключить дифференциальные входы данных (DIN и nDIN) к дифференциальным выходам данных (DOUT и nDOUT) предыдущей микросхемы. Входы DIN, nDIN первой микросхемы в цепочке следует подключить к шине «Общий». Схема подключения с использованием интерфейса DCH изображена на рисунке 12.

Рисунок 12 – Подключение нескольких АЦП в единую цепочку

Рисунок 13 – Диаграмма чтения данных при использовании нескольких АЦП

Рисунок 14 – Диаграмма чтения данных при использовании одного АЦП

Таблица 15 – Временные параметры при чтении данных

| Наименование параметра,                                                            | Буквенное   | Значение і | параметра |

|------------------------------------------------------------------------------------|-------------|------------|-----------|

| единица измерения                                                                  | обозначение | не менее   | не более  |

| Время задержки сигнала NDVALID относительно отрицательного фронта сигнала CLK, нс  | T1          | -          | 25        |

| Время задержки сигнала NDVALID относительно отрицательного фронта сигнала DCLK, нс | T2          | -          | 25        |

| Время задержки сигнала DOUT относительно отрицательного фронта сигнала DCLK, нс    | Т3          | -          | 25        |

| Время установки данных относительно отрицательного фронта сигнала NDVALID, нс      | T4          | 50         | -         |

| Время установки данных относительно отрицательного фронта сигнала DCLK, нс         | T5          | 5          | -         |

| Время удержания данных относительно отрицательного фронта сигнала DCLK, нс         | T6          | 5          | -         |

#### 5.4.2 Режим преобразования тока с внутренним управлением (MDS = 001)

В этом режиме микросхема измеряет втекающие токи на входах AIN1-8 путем накопления зарядов на интеграторах и последующей оцифровки накопленного значения с помощью сигма-дельта АЦП. В отличие от режима MDS = 000 управление осуществляется только через интерфейс SPI.

Логические состояния на выводах микросхемы RANGE0-2, CLK\_4X, CONV, FORMAT игнорируются. Конфигурация определяется значениями внутренних регистров микросхемы.

Биты RANGE[2:0] определяют шкалу интегрирования.

Бит CLKS определяет источник тактовой частоты.

Бит CLK4 определяет коэффициент деления тактовой частоты.

Бит FRMT определяет разрядность данных при чтении по шине SPI.

Бит CONV определяет начальное состояние сигнала управления CONV.

Управление интегрированием и преобразованием входного аналогового сигнала выполняется тем же автоматом с конечным числом состояний, который используется и в режиме MDS = 000.

Время интегрирования определяется значением регистра длительности интегрирования TINT. Если время преобразования меньше значения регистра TINT, микросхема функционирует в режиме постоянного интегрирования. Если время полного цикла преобразования больше значения регистра TINT — в режиме периодического интегрирования.

Диаграмма функционирования микросхемы в режиме постоянного интегрирования показана на рисунке 10, в режиме периодического интегрирования на рисунке 11. Значения временных параметров приведены в таблице 14.

По окончании преобразования формируется выходной сигнал NDVALID. Чтение результатов преобразования производится только по шине SPI. Интерфейс DCH не функционирует.

#### 5.4.3 Режим преобразования положительного напряжения (MDS=010)

Данный режим функционирования является режимом преобразования положительного напряжения от 0 до  $U_{REF}$  (2,4 B), при котором на вход сигма-дельта АЦП каналов 1-8 подается напряжение с дополнительных аналоговых входов по напряжению VIN1-8 соответственно. Интеграторы тока для входов AIN1-8 выключены.

Управление микросхемой в этом режиме производится только через интерфейс SPI. Конфигурация определяется значениями внутренних регистров.

Бит CLKS определяет источник тактовой частоты.

Бит REFS определяет источник шкалы АЦП.

Бит CLK4 определяет коэффициент деления тактовой частоты.

Бит FRMT определяет разрядность данных.

В режиме MDS=010 автомат с конечным числом состояний, изображенный на рисунке 9, не используется. Преобразование напряжения всегда производится в непрерывном режиме. Время первого преобразования равно Т1, время последующих преобразований равно Т2 (см. таблицу 14). Любая запись в регистр CFG сбрасывает цифровой фильтр, и преобразование начинается заново. Преобразование, последующее после записи в CFG, считается первым.

По окончании любого преобразования формируется выходной сигнал NDVALID. После чтения из любого регистра DATA1-8 по SPI он сбрасывается. Чтение результатов преобразования производится только по шине SPI. Интерфейс DCH не функционирует.

#### 5.4.4 Режим преобразования дифференциального напряжения (MDS=100)

Данный режим функционирования является режимом преобразования дифференциального напряжения от -UREF (-2,4 B) до UREF (2,4 B), при котором на входы сигма-дельта АЦП каналов 1, 3, 5, 7 подается напряжения с дополнительных аналоговых входов по напряжению VIN1-2, VIN3-4, VIN5-6, VIN7-8 соответственно. Т.е. четные и нечетные входы VIN попарно объединяются, образуя дифференциальные входы по напряжению. Интеграторы тока для входов AIN1-8 выключены.

Управление микросхемой в этом режиме производится только через интерфейс SPI. Конфигурация определяется значениями внутренних регистров.

Бит CLKS определяет источник тактовой частоты.

Бит REFS определяет источник шкалы АЦП.

Бит CLK4 определяет коэффициент деления тактовой частоты.

Бит FRMT определяет разрядность данных.

В режиме MDS=010 автомат с конечным числом состояний, изображенный на рисунке 9, не используется. Преобразование напряжения всегда производится в непрерывном режиме. Время первого преобразования равно Т1, время последующих преобразований равно Т2 (см. таблицу 16). Любая запись в регистр CFG сбрасывает цифровой фильтр, и преобразование начинается заново. Преобразование, последующее после записи в регистр CFG, считается первым.

По окончании любого преобразования формируется выходной сигнал NDVALID. После чтения из любого регистра DATA1-8 по SPI он сбрасывается. Чтение результатов преобразования производится только по шине SPI. Интерфейс DCH не функционирует.

#### 5.4.4.1 Описание цифрового фильтра

Рисунок 15 – Структурная схема цифрового фильтра

Цифровой фильтр состоит из последовательно соединенных фильтра Sinc<sup>3</sup> и схемы усреднения полученных результатов.

Частота выходных данных и время стабилизации выходных данных цифрового фильтра определяются частотой F<sub>CLK</sub> и значениями битов FS[3:0]. Зависимости частоты выходных данных и времени стабилизации от значения FS представлены в таблице 16.

| Таблица 16 – Временные параметры в режимах преобра: | азования напряжения |

|-----------------------------------------------------|---------------------|

|-----------------------------------------------------|---------------------|

| Значение |                |                | Частота        | Частота            |

|----------|----------------|----------------|----------------|--------------------|

| FS       | преобразования | преобразований | последующих    | сэмплирования на   |

|          | Т1, мкс        | Т2, мкс        | преобразований | входе Fsample, МГц |

| 0000     | 716            | 336            | 2,97 КГц       | 2                  |

| 0001     | 428            | 192            | 5,2 КГц        | 2                  |

| 0010     | 620            | 288            | 3,47 КГц       | 2                  |

| 0011     | 812            | 384            | 2,6 КГц        | 2                  |

| 0100     | 1004           | 480            | 2,08 КГц       | 2                  |

| 0101     | 2005,5         | 960            | 1,04 КГц       | 1                  |

| 0110     | 3925,5         | 1920           | 520,8 Гц       | 1                  |

| 0111     | 15445,5        | 5120           | 195,3 Гц       | 1                  |

| 1000     | 30805,5        | 10240          | 97,6 Гц        | 1                  |

| 1001     | 61525,5        | 20480          | 48,8 Гц        | 1                  |

| 1010     | 122965,5       | 40960          | 24,4 Гц        | 1                  |

| 1011     | 307285,5       | 102400         | 9,76 Гц        | 1                  |

| 1100     | 614485,5       | 204800         | 4,88 Гц        | 1                  |

| 1101     | 983125,5       | 327680         | 3,05 Гц        | 1                  |

| 1110     | 1966248,5      | 655360         | 1,52 Гц        | 0,5                |

| 1111     | 3932328,5      | 1310720        | 0,76 Гц        | 0,5                |

#### Примечания

<sup>1</sup> Время первого преобразования и время последующих преобразований приведены при внешней тактовой частоте 4 МГц.

<sup>2</sup> Время первого преобразования представляет собой интервал времени от момента запуска цифрового фильтра до момента записи первого результата преобразования в контроллер шины SPI.

<sup>3</sup> Время последующих преобразований представляет собой интервал времени между моментами записи последовательных результатов преобразования в контроллер шины SPI

#### 5.4.5 Режим пониженного потребления (MDS=011)

Данный режим предназначен для снижения тока потребления АЦП в случае, если преобразование в данный момент времени не используется.

Для достижения минимального тока потребления все внешние сигналы тактовой частоты должны быть выключены. Все цифровые входы должны быть подключены к шине «Общий» или к шине «Питание».

Время перехода из режима пониженного потребления в режим преобразования до 30 мкс.

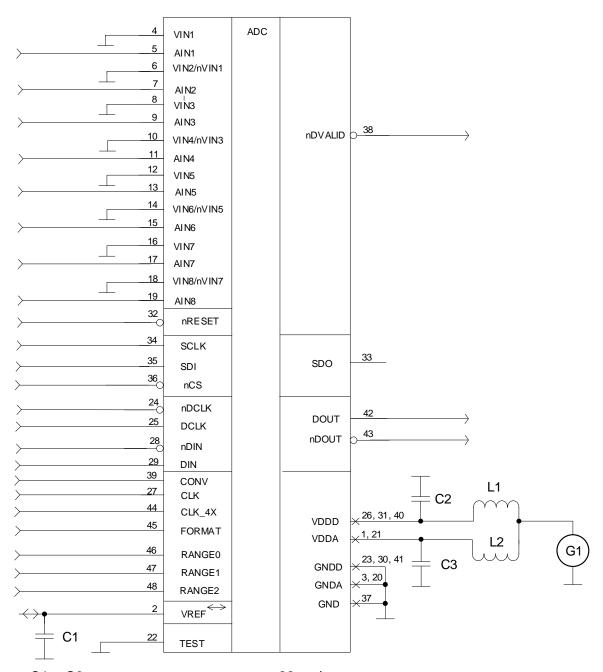

## 6 Типовые схемы включения

С1 – С3 – конденсаторы ёмкостью 22 мкФ;

G1 – источник напряжения питания (3,3 ± 0,3) В;

L1, L2 – катушки индуктивностью 13 мГн.

Рисунок 16 – Типовая схема включения микросхем в режиме преобразования тока

С1 – С3 – конденсаторы ёмкостью 22 мкФ;

G1 – источник напряжения питания  $(3,3 \pm 0,3)$  В;

L1, L2 – катушки индуктивностью 13 мГн.

Рисунок 17 – Типовая схема включения микросхем в режиме преобразования напряжения

## 7 Типовые зависимости

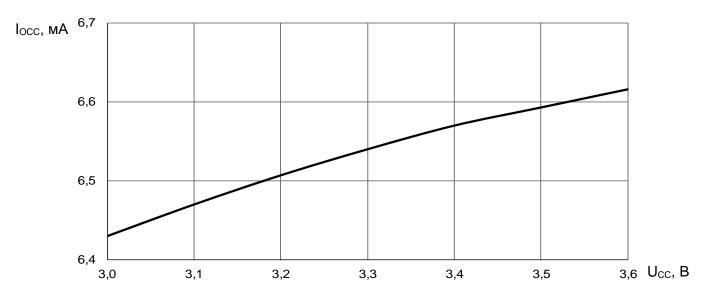

Рисунок 18 – Зависимость динамического тока потребления от напряжения питания в режиме преобразования напряжения (MDS=010), с внешним тактовым сигналом fc = 4 МГц, внешним опорным напряжением U<sub>REF</sub> = 2,4 B, T = 25 °C

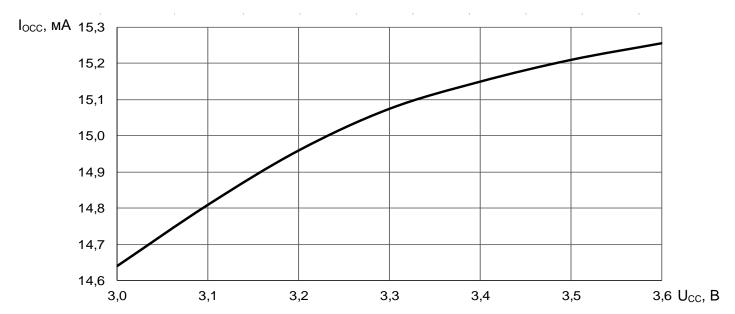

Рисунок 19 — Зависимость динамического тока потребления от напряжения питания в режиме преобразования тока (MDS=001), с внешним тактовым сигналом  $f_C = 4$  МГц, внешним опорным напряжением  $U_{REF} = 2.4$  В, T = 25 °C

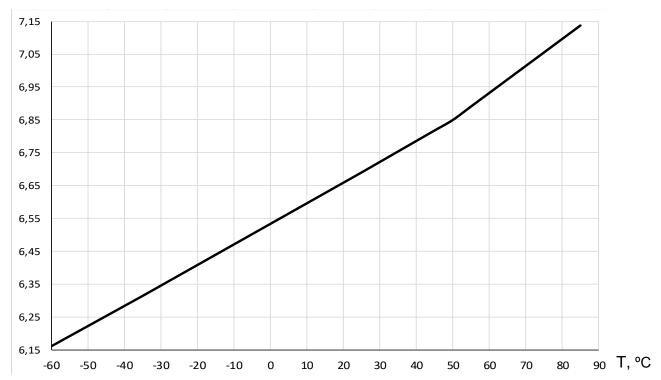

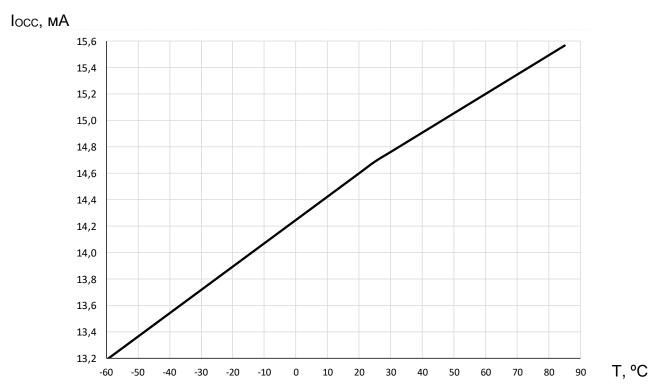

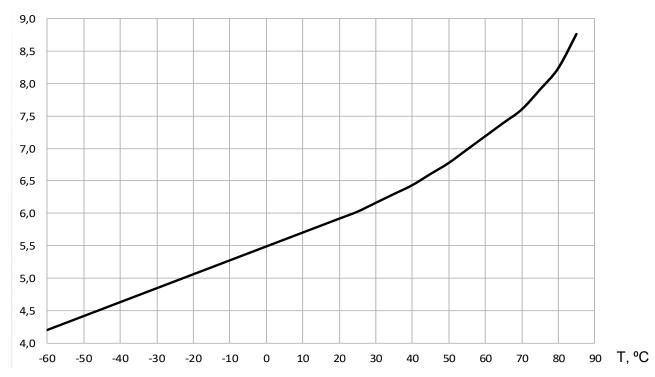

Рисунок 20 — Зависимость динамического тока потребления от температуры в режиме преобразования напряжения (MDS=010), при  $f_C = 4$  МГц,  $U_{REF} = 2.4$  В при  $U_{CC} = 3.3$  В,  $U_{IH} = 3.3$  В,  $U_{IL} = 0$  В

Рисунок 21 — Зависимость динамического тока потребления от температуры в режиме преобразования тока (MDS=001), при  $f_C$  = 4 МГц,  $U_{REF}$  = 2,4 В при  $U_{CC}$  = 3,3 В,  $U_{IL}$  = 0 В

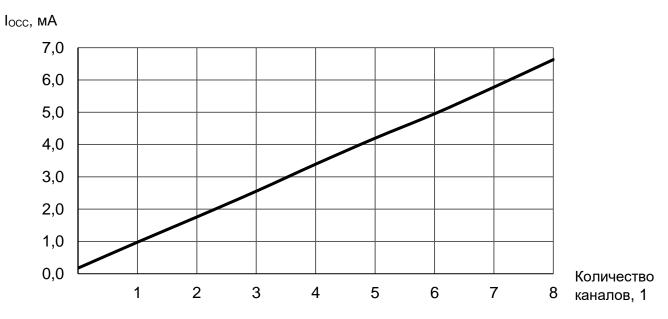

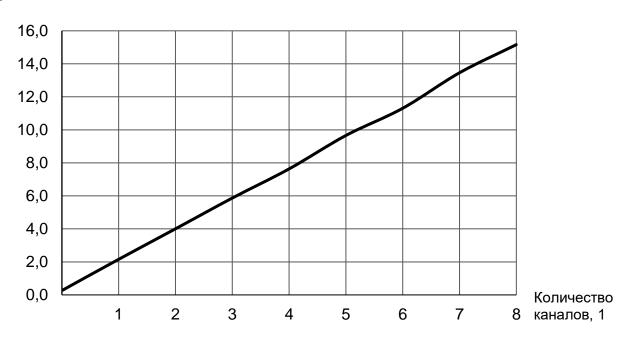

Рисунок 22 — Зависимость динамического тока потребления от количества включенных каналов в режиме преобразования напряжения (MDS=010), при  $f_C=4$  МГц, внешним опорным напряжением  $U_{REF}=2.4$  В при  $U_{CC}=3.6$  В,  $U_{IH}=3.6$  В,  $U_{IL}=0$  В, T=25 °C

Рисунок 23 — Зависимость динамического тока потребления от количества включенных каналов в режиме преобразования тока (MDS=001), при  $f_C$  = 4 МГц,  $U_{REF}$  = 2,4 В при  $U_{CC}$  = 3,6 B,  $U_{IH}$  = 3,6 B,  $U_{IL}$  = 0 B, T = 25 °C

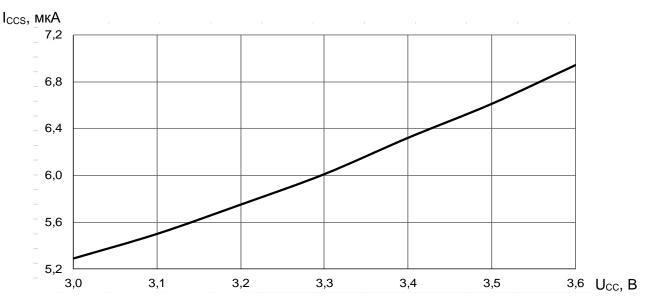

Рисунок 24 — Зависимость тока потребления в режиме пониженного энергопотребления от напряжения питания при T = 25 °C

Рисунок 25 – Зависимость тока потребления в режиме пониженного энергопотребления от температуры при Ucc = 3,3 B

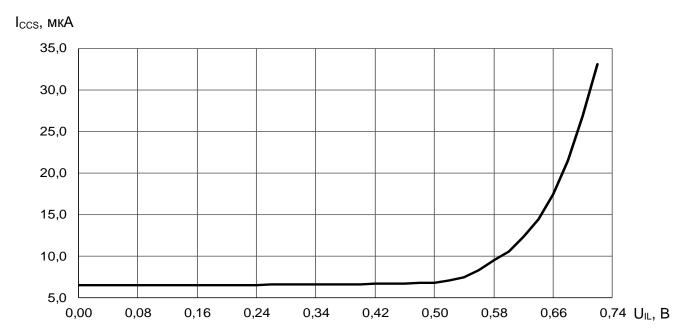

Рисунок 26 — Зависимость тока потребления в режиме пониженного энергопотребления от входного напряжения низкого уровня при  $U_{CC}=3,6~B,~T=25~^{\circ}C$

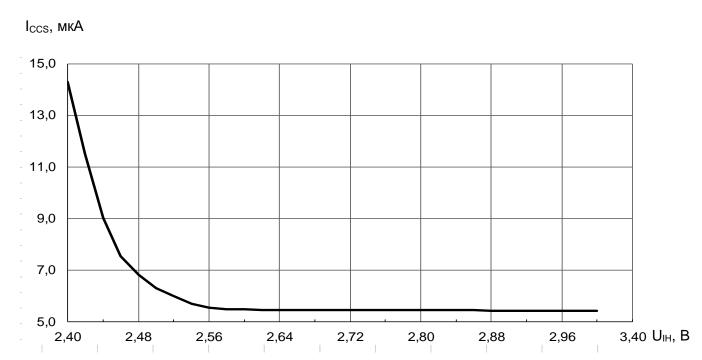

Рисунок 27 – Зависимость тока потребления в режиме пониженного энергопотребления от входного напряжения высокого уровня при Ucc = 3,0 B, T = 25 °C

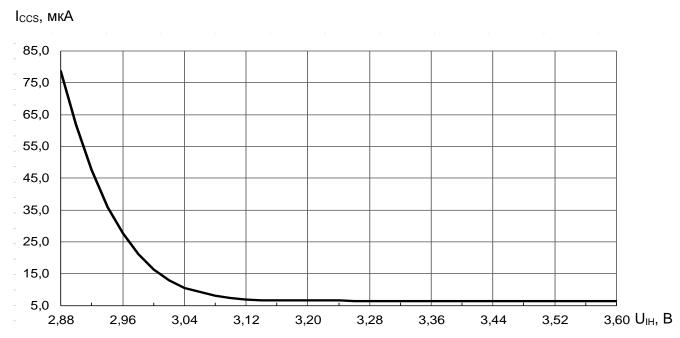

Рисунок 28 — Зависимость тока потребления в режиме пониженного энергопотребления от уровня входного напряжения высокого уровня при  $U_{CC}$  = 3,6 B, T = 25 °C

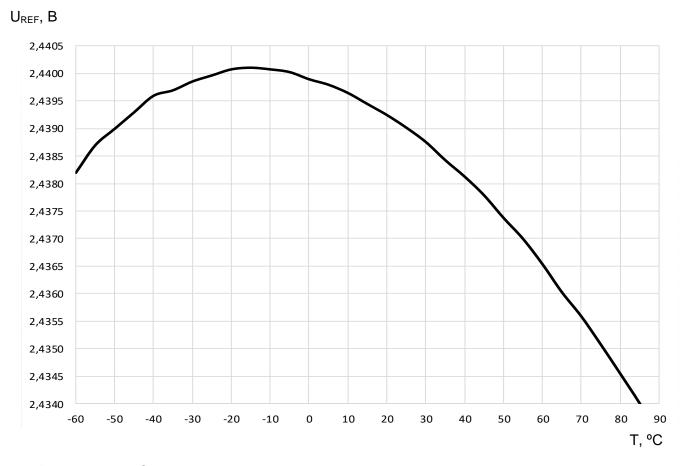

Рисунок 29 — Зависимость выходного опорного напряжения внутреннего источника опорного напряжения от температуры при  $U_{CC}$  = 3,3 B

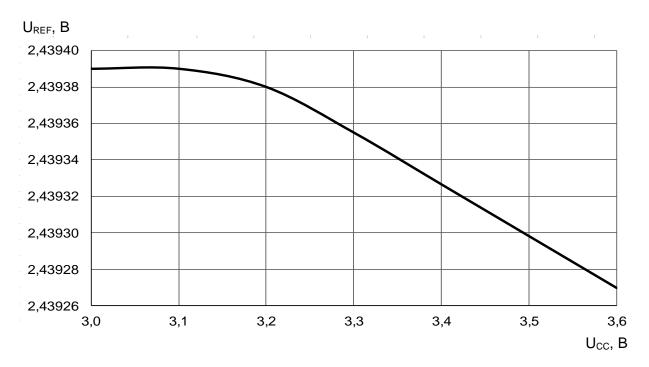

Рисунок 30 – Зависимость выходного напряжения внутреннего источника опорного напряжения от напряжения питания при T = 25 °C

# 8 Электрические параметры микросхем

Таблица 17 – Электрические параметры микросхем при приемке и поставке

| Наименование параметра,<br>единица измерения,                                                                                                                                 | Буквенное<br>обозначение<br>параметра | Норма<br>параметра    |           | Темпе-<br>ратура |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|-----------|------------------|

| режим измерения                                                                                                                                                               | Букв<br>обозн<br>пара                 | не менее              | не более  | среды,<br>°С     |

| Выходное напряжение низкого уровня, В, на<br>выводах SDO, nVALID, DOUT, nDOUT                                                                                                 | U <sub>OL</sub>                       | _                     | 0,1 • Ucc | 25,              |

| Выходное напряжение высокого уровня, В, на<br>выводах SDO, nVALID, DOUT, nDOUT                                                                                                | U <sub>ОН</sub>                       | 0,9 • U <sub>CC</sub> | -         | 85,<br>- 60      |

| Напряжение смещения, мВ                                                                                                                                                       | U <sub>IO</sub>                       | -3,0                  | 3,0       |                  |

| Входной ток смещения, пА,                                                                                                                                                     | I <sub>BIAS</sub>                     | _                     | 1,0       | 25               |

| по входам AIN1 – AIN8                                                                                                                                                         |                                       | _                     | 10        | 85               |

| Динамический ток потребления, мА                                                                                                                                              | locc                                  | -                     | 60        |                  |

| Ток потребления в режиме пониженного<br>энергопотребления, мкА                                                                                                                | Iccs                                  | _                     | 100       |                  |

| Входной ток утечки низкого уровня, мкА,<br>по входам TEST, nDCLK, DCLK, CLK, nDIN, DIN,<br>nRESET, SCLK, SDIN, nCS, CONV, CLK_4X,<br>FORMAT, RANGE0, RANGE1, RANGE2           | I <sub>ILL</sub>                      | -10                   | 10        |                  |

| Входной ток утечки высокого уровня, мкА,<br>по входам TEST, nDCLK, DCLK, CLK, nDIN, DIN,<br>nRESET, SCLK, SDIN, nCS, CONV, CLK_4X,<br>FORMAT, RANGE0, RANGE1, RANGE2          | IILH                                  | -10                   | 10        |                  |

| Максимальное значение накопленного заряда, пКл,                                                                                                                               |                                       |                       |           |                  |

| при U <sub>REF</sub> = 2,4 В:                                                                                                                                                 |                                       |                       |           |                  |

| диапазон 0                                                                                                                                                                    | $Q_0$                                 | 10,0                  | 14,0      |                  |

| диапазон 1                                                                                                                                                                    | $Q_1$                                 | 47,5                  | 52,5      | 25               |

| диапазон 2                                                                                                                                                                    | $Q_2$                                 | 95,0                  | 105,0     | 25,<br>85,       |

| диапазон 3                                                                                                                                                                    | $Q_3$                                 | 142,5                 | 157,5     | <b>–</b> 60      |

| диапазон 4                                                                                                                                                                    | $Q_4$                                 | 190,0                 | 210,0     |                  |

| диапазон 5                                                                                                                                                                    | $Q_5$                                 | 237,5                 | 262,5     |                  |

| диапазон 6                                                                                                                                                                    | $Q_6$                                 | 285,0                 | 315,0     |                  |

| диапазон 7                                                                                                                                                                    | Q <sub>7</sub>                        | 332,5                 | 367,5     |                  |

| Отношение сигнал/шум + искажения АЦП, дБ,<br>при U <sub>REF</sub> = 2,4 B, MDS = 100, FS = 0101,<br>дифференциальный входной сигнал амплитудой<br>минус 1 дБ, частотой 171 Гц | SNDR                                  | 85                    | _         |                  |

| Погрешность в конечной точке характеристики преобразования АЦП, %, при U <sub>REF</sub> = 2,4 В                                                                               | E <sub>G</sub>                        | -1                    | 1         |                  |

| Выходная частота внутреннего RC-генератора, МГц                                                                                                                               | fo                                    | 3,9                   | 4,2       |                  |

| Разрешающая способность АЦП, разрядов                                                                                                                                         | N                                     | _                     | 20        |                  |

Микросхемы устойчивы к воздействию статического электричества с потенциалом не менее 2 000 В.

# 9 Предельно-допустимые и предельные параметры

Таблица 18 – Предельно-допустимые электрические режимы эксплуатации и предельные электрические режимы микросхем

|                                                                             | a 4e                                  | Норма параметра                   |                  |                     |                       |

|-----------------------------------------------------------------------------|---------------------------------------|-----------------------------------|------------------|---------------------|-----------------------|

| Наименование параметра,<br>единица измерения                                | Буквенное<br>обозначение<br>параметра | Предельно-<br>допустимый<br>режим |                  | Предельный<br>режим |                       |

|                                                                             |                                       | не<br>менее                       | не<br>более      | не<br>менее         | не<br>более           |