# Микросхема ЭСППЗУ с параллельным/последовательным вводом/выводом информации Flash-типа 16 МБит, К1636РР4У

# Основные характеристики микросхемы

- Наличие двух последовательных и параллельного интерфейсов;

- Совместимость по входам с 5 В («5 В толерантность»);

- Восемь секторов по 2 Мбит;

- 1024 страницы по 16 Кбит;

- Возможность стирания страницы, любой комбинации секторов и всей памяти;

- Функция защиты сектора от стирания и записи: аппаратная проверка сектора для предотвращения стирания и записи;

- Уменьшение времени программирования при повторяющихся программных командных последовательностях (режим bypass);

- Аппаратный алгоритм автоматического стирания и верификации всей памяти или желаемого количества секторов;

- Аппаратный алгоритм автоматической верификации и записи данных по указанному адресу;

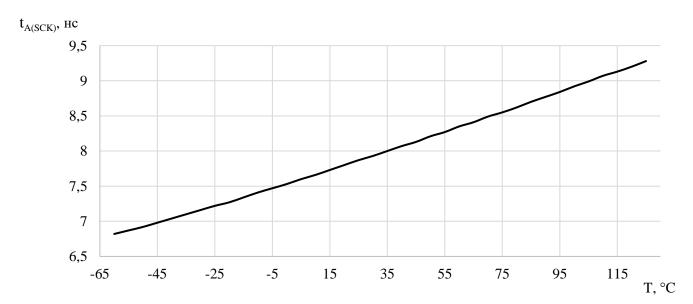

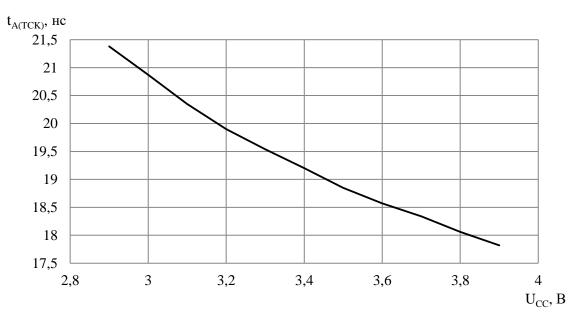

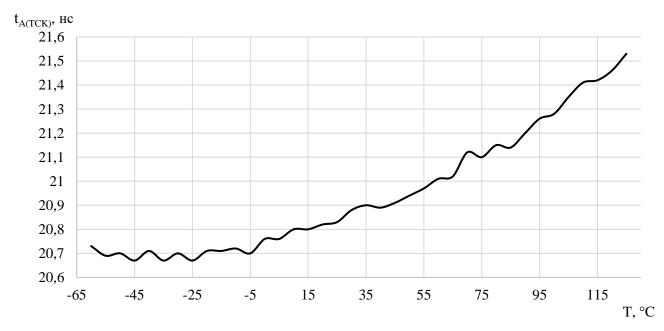

- Программный метод детектирования окончания циклов стирания и записи;

- Встроенная схема формирования высоковольтного напряжения программирования и стирания;

- Встроенная схема сброса при включении питания;

- Время сохранения данных 13 лет;

- 10 000 циклов записи/стирания данных;

- Напряжение питания от 3,0 до 3,6 В;

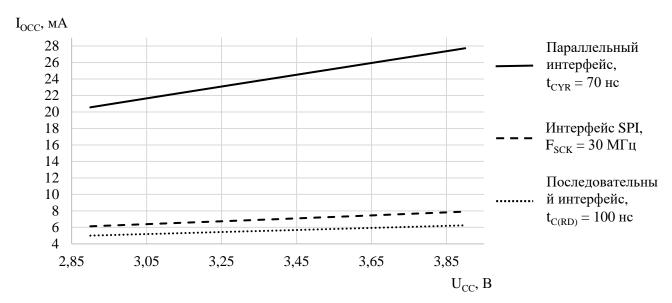

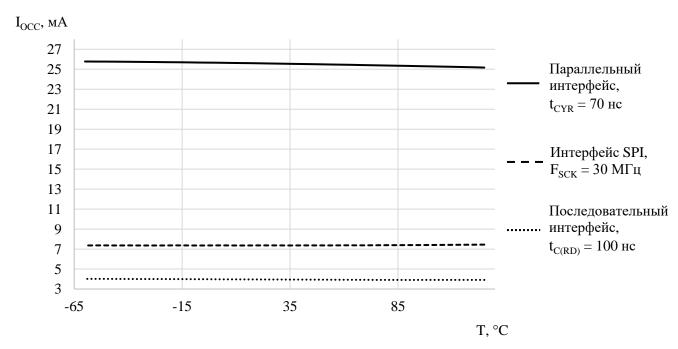

- Ток потребления в режиме хранения не более 1 мА;

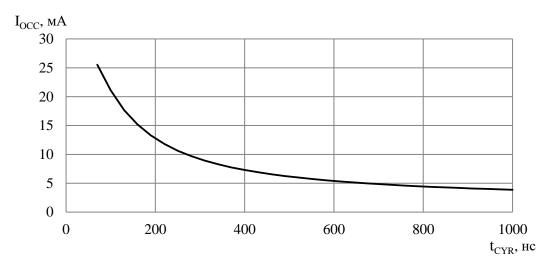

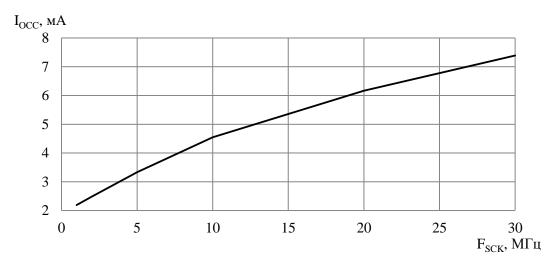

- Динамический ток потребления не более 50 мА;

- Время выборки адреса не более 55 нс;

- Рабочий диапазон температур от − 60 °C до 125 °C.

ГГ – год выпуска НН – неделя выпуска

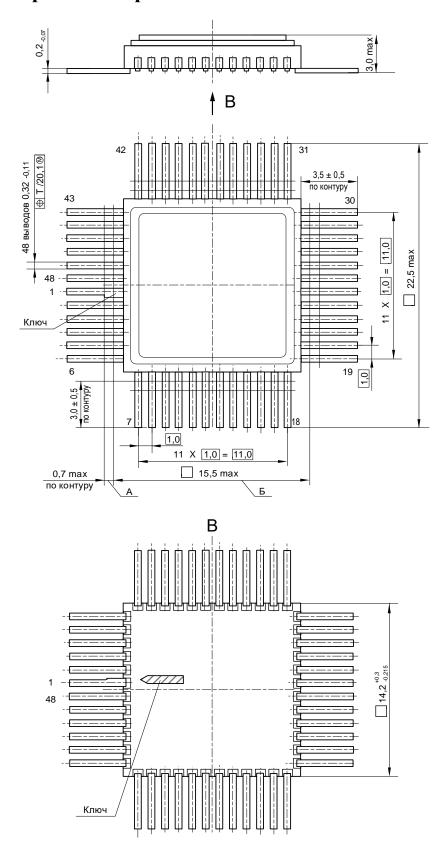

## Тип корпуса:

48-выводной металлокерамический корпус H16.48-1B.

Масса микросхем не более 2,0 г.

## Общее описание и область применения микросхемы

Микросхемы интегральные К1636РР4У (далее – микросхемы) представляют собой энергонезависимые запоминающие устройства типа «Flash» информационной емкостью 16 Мбит с количеством циклов перезаписи до нескольких десятков тысяч.

Микросхемы предназначены для хранения и оперативной модификации массивов данных и программного обеспечения.

# Содержание

| 1  | Стр | уктурна  | ая блок-схема                                       | 3  |

|----|-----|----------|-----------------------------------------------------|----|

| 2  | Усл | овное г  | рафическое обозначение                              | 4  |

| 3  | Опи | исание в | выводов                                             | 5  |

| 4  | Ука | зания п  | о применению и эксплуатации                         | 7  |

| 5  | Опи | исание ф | рункционирования                                    | 8  |

|    | 5.1 | Режим    | параллельного интерфейса                            | 8  |

|    |     | 5.1.1    | Поддерживаемые операции на шине памяти              | 8  |

|    |     | 5.1.2    | Требования, предъявляемые при чтении данных         | 9  |

|    |     | 5.1.3    | Команды записи и командные последовательности       | 9  |

|    |     | 5.1.4    | Режим хранения                                      | 10 |

|    |     | 5.1.5    | Режим «Autoselect»                                  | 10 |

|    |     | 5.1.6    | Установка и снятие защиты с сектора                 | 11 |

|    |     | 5.1.7    | Аппаратная защита данных                            | 11 |

|    |     | 5.1.8    | Описание команд                                     | 12 |

|    |     | 5.1.9    | Статус операции программирования / стирания         | 18 |

|    | 5.2 | Режим    | последовательного интерфейса FLASH                  | 24 |

|    |     | 5.2.1    | Командные последовательности                        | 25 |

|    | 5.3 | Послед   | довательный интерфейс SPI                           | 30 |

|    |     | 5.3.1    | Команды и адресация                                 | 30 |

|    |     | 5.3.2    | Операция чтения массива данных                      | 31 |

|    |     | 5.3.3    | Операция программирования байта                     | 32 |

|    |     | 5.3.4    | Операция стирания сектора                           | 33 |

|    |     | 5.3.5    | Операция стирания всей памяти                       | 34 |

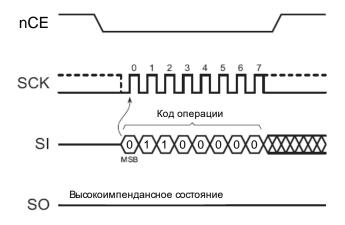

|    |     | 5.3.6    | Операция разрешения записи                          | 35 |

|    |     | 5.3.7    | Операция запрета записи                             | 36 |

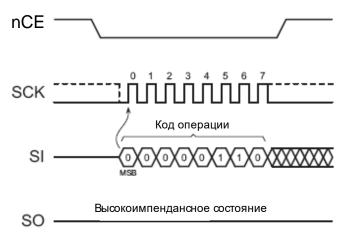

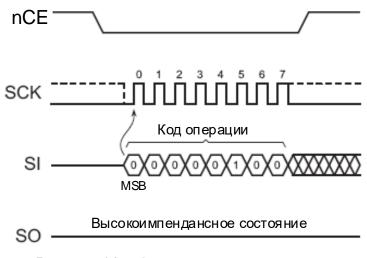

|    |     | 5.3.8    | Операция установки защиты сектора                   | 36 |

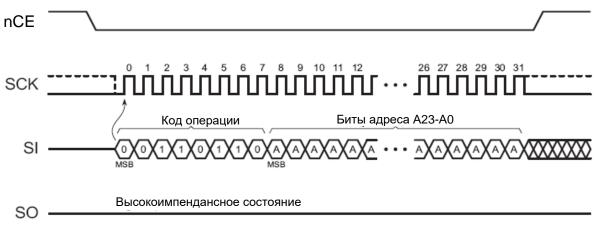

|    |     | 5.3.9    | Операция снятия защиты сектора                      | 38 |

|    |     | 5.3.10   | Операция чтения регистра защиты сектора             | 39 |

|    |     | 5.3.11   | Операция чтения регистра статуса                    | 39 |

|    |     | 5.3.12   | Операция записи регистра статуса                    | 42 |

|    |     | 5.3.13   | Операция сброса                                     | 43 |

|    |     | 5.3.14   | Операция чтения ID кодов производителя и микросхемы | 44 |

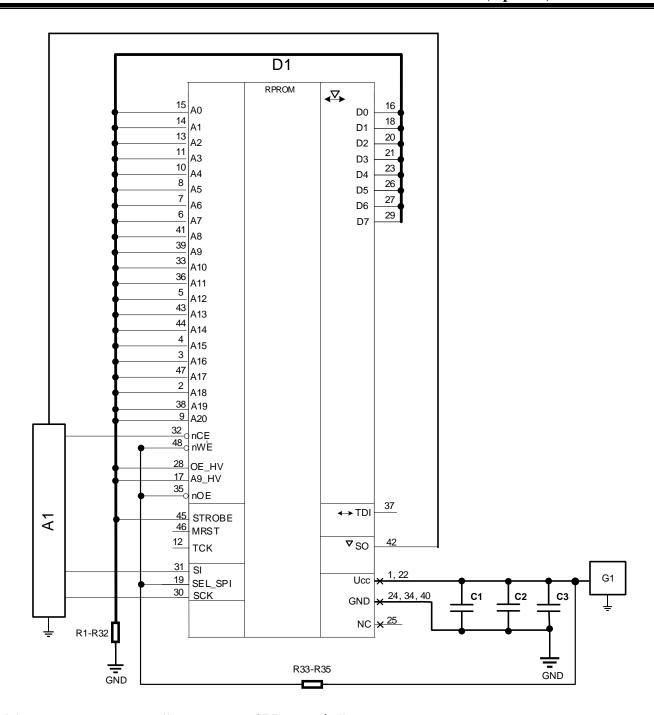

| 6  | Тип | овые сх  | кемы включения микросхем                            | 45 |

| 7  | Bpe | менные   | диаграммы                                           | 48 |

| 8  | Эле | ктричес  | ские параметры                                      | 52 |

| 9  |     |          | допустимые и предельные параметры                   |    |

| 10 | Спр | авочны   | е данные                                            | 56 |

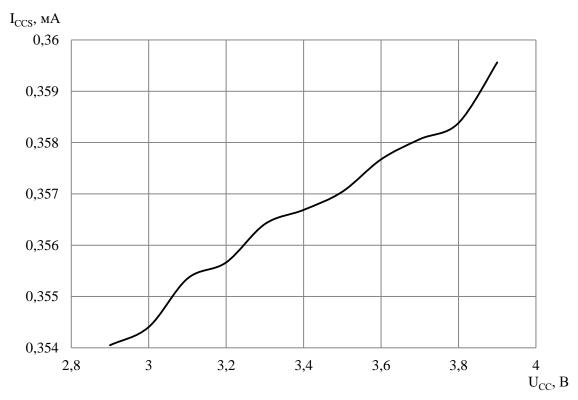

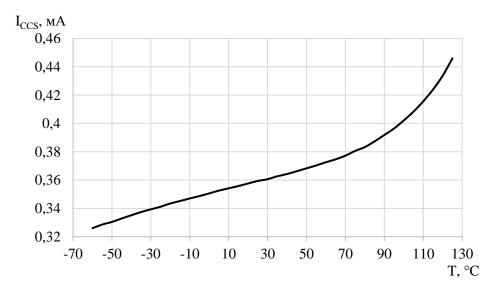

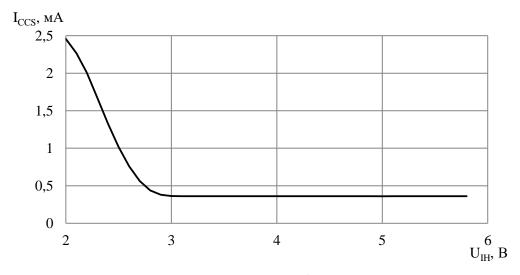

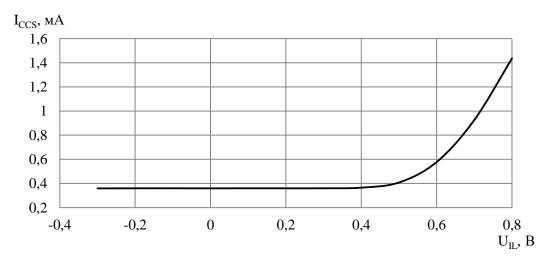

| 11 | Тип | ювые за  | висимости                                           | 58 |

| 12 | Габ | аритныі  | й чертеж                                            | 70 |

| 13 | Инф | рормаци  | ия для заказа                                       | 71 |

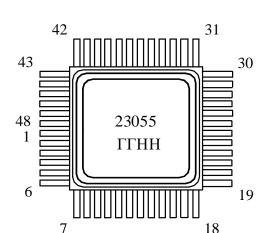

## 1 Структурная блок-схема

Рисунок 1 – Структурная блок-схема

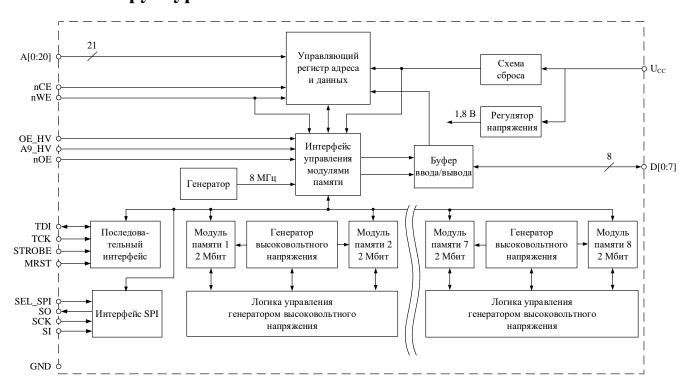

## 2 Условное графическое обозначение

Рисунок 2 – Условное графическое обозначение

## 3 Описание выводов

$T \, a \, б \, \pi \, u \, ц \, a \, 1 \, - O$ писание выводов

| Номер<br>вывода<br>корпуса | Обозначение<br>вывода | Назначение вывода                                        |

|----------------------------|-----------------------|----------------------------------------------------------|

| 1                          | $U_{CC}$              | Питание                                                  |

| 2                          | A18                   | Вход адреса                                              |

| 3                          | A16                   | Вход адреса                                              |

| 4                          | A15                   | Вход адреса                                              |

| 5                          | A12                   | Вход адреса                                              |

| 6                          | A7                    | Вход адреса                                              |

| 7                          | A6                    | Вход адреса                                              |

| 8                          | A5                    | Вход адреса                                              |

| 9                          | A20                   | Вход адреса                                              |

| 10                         | A4                    | Вход адреса                                              |

| 11                         | A3                    | Вход адреса                                              |

| 12                         | TCK                   | Вход синхросигнала последовательного интерфейса          |

| 13                         | A2                    | Вход адреса                                              |

| 14                         | A1                    | Вход адреса                                              |

| 15                         | A0                    | Вход адреса                                              |

| 16                         | D0                    | Вход/выход параллельных данных                           |

| 17                         | A9_HV                 | Вход режима установки/снятия защиты от записи и стирания |

|                            |                       | (активный высокий уровень)                               |

| 18                         | D1                    | Вход/выход параллельных данных                           |

| 19                         | SEL_SPI               | Вход выбора интерфейса SPI (активный высокий уровень)    |

| 20                         | D2                    | Вход/выход параллельных данных                           |

| 21                         | D3                    | Вход/выход параллельных данных                           |

| 22                         | Ucc                   | Питание                                                  |

| 23                         | D4                    | Вход/выход параллельных данных                           |

| 24                         | GND                   | Общий                                                    |

| 25                         | NC                    | Не используется                                          |

| 26                         | D5                    | Вход/выход параллельных данных                           |

| 27                         | D6                    | Вход/выход параллельных данных                           |

| 28                         | OE_HV                 | Вход режима установки/снятия защиты от записи и стирания |

|                            |                       | (активный высокий уровень)                               |

| 29                         | D7                    | Вход/выход параллельных данных                           |

| 30                         | SCK                   | Вход синхросигнала интерфейса SPI                        |

| 31                         | SI                    | Вход данных интерфейса SPI                               |

| 32                         | nCE                   | Вход разрешения выборки (активный низкий уровень)        |

| 33                         | A10                   | Вход адреса                                              |

| 34                         | GND                   | Общий                                                    |

| 35                         | nOE                   | Вход разрешения чтения-(активный низкий уровень)         |

| Номер<br>вывода<br>корпуса | Обозначение<br>вывода | Назначение вывода                                                  |  |  |  |  |  |  |  |  |  |

|----------------------------|-----------------------|--------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 36                         | A11                   | Вход адреса                                                        |  |  |  |  |  |  |  |  |  |

| 37                         | TDI                   | Вход/выход данных последовательного интерфейса                     |  |  |  |  |  |  |  |  |  |

| 38                         | A19                   | Вход адреса                                                        |  |  |  |  |  |  |  |  |  |

| 39                         | A9                    | Вход адреса                                                        |  |  |  |  |  |  |  |  |  |

| 40                         | GND                   | Общий                                                              |  |  |  |  |  |  |  |  |  |

| 41                         | A8                    | Вход адреса                                                        |  |  |  |  |  |  |  |  |  |

| 42                         | SO                    | Выход данных интерфейса SPI                                        |  |  |  |  |  |  |  |  |  |

| 43                         | A13                   | Вход адреса                                                        |  |  |  |  |  |  |  |  |  |

| 44                         | A14                   | Вход адреса                                                        |  |  |  |  |  |  |  |  |  |

| 45                         | STROBE                | Вход инициирования обмена по последовательному интерфейсу          |  |  |  |  |  |  |  |  |  |

| 46                         | MRST                  | Вход сброса последовательного интерфейса (активный низкий уровень) |  |  |  |  |  |  |  |  |  |

| 47                         | A17                   | Вход адреса                                                        |  |  |  |  |  |  |  |  |  |

| 48                         | nWE                   | Вход разрешения записи (активный низкий уровень)                   |  |  |  |  |  |  |  |  |  |

## 4 Указания по применению и эксплуатации

При ремонте аппаратуры и измерении параметров замену микросхем необходимо проводить только при отключенных источниках питания.

Инструмент для пайки (сварки) и монтажа не должен иметь потенциал, превышающий 0,3 В относительно шины общий.

Запрещается подведение каких-либо электрических сигналов (в том числе шин питание, общий) к выводам микросхем, не используемым согласно таблице 1.

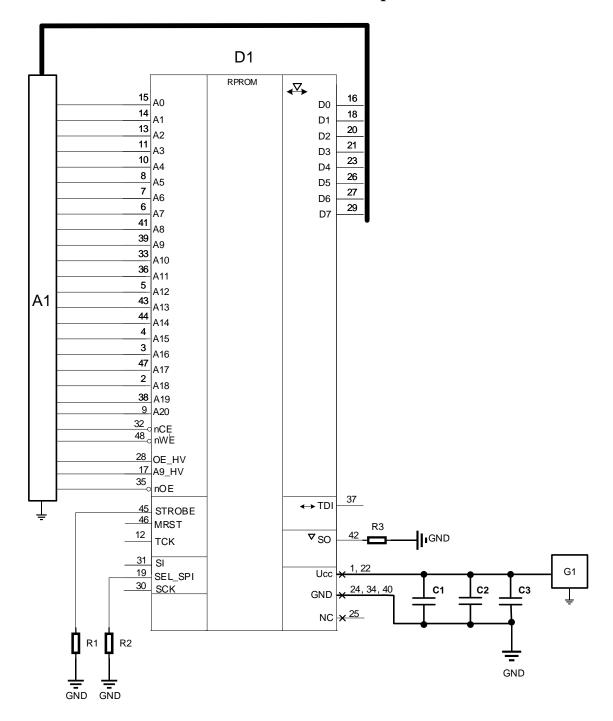

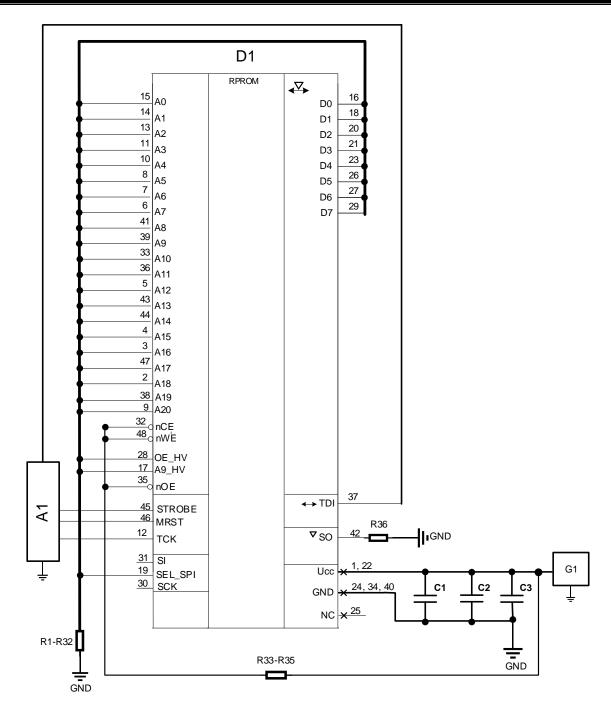

Типовые схемы включения микросхемы приведены на рисунках 28 - 30.

Крышка микросхем электрически соединена с выводом 24 (общий).

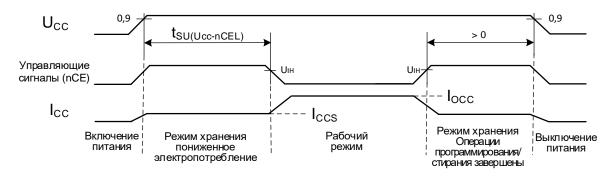

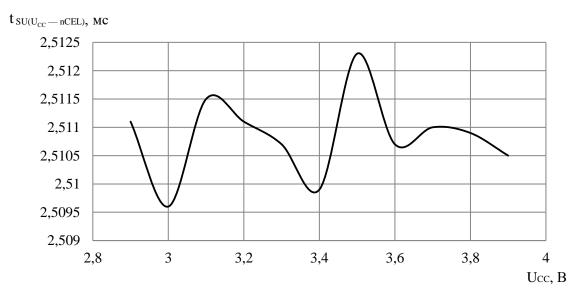

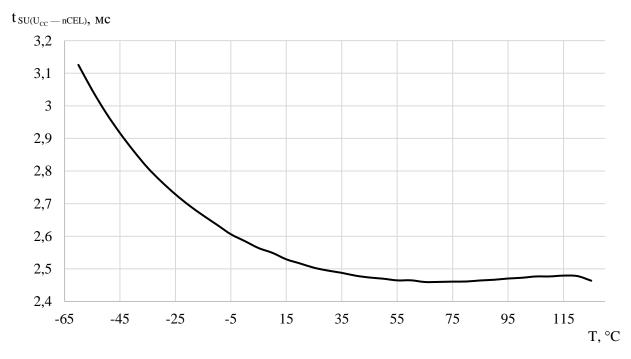

Длительность фронта напряжения питания при включении микросхемы не менее 10 мкс. После достижения напряжением питания уровня 90 % и до первого обращения к памяти микросхемы рекомендуется выдержать время не менее t<sub>SU(Ucc-nCEL)</sub>.

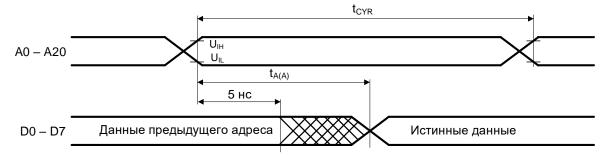

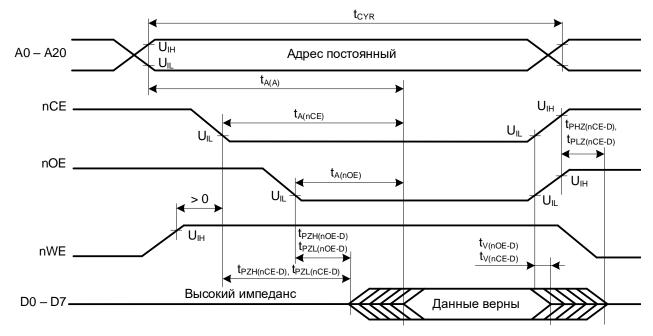

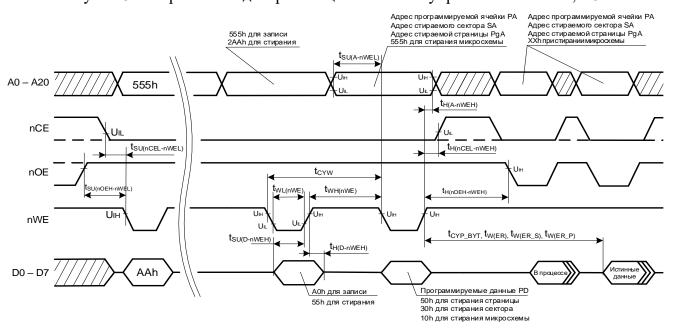

Временные диаграммы работы микросхем приведены на рисунках 31 - 39.

Динамические параметры микросхемы, установленные в таблицах 13, 14, гарантируются при времени нарастания/спада входных сигналов не более 10 нс. Допускается функционирование микросхем при времени нарастания/спада входных сигналов до 100 нс без гарантии динамических параметров.

Запрещается производить запись по одному и тому же адресу более одного раза без предшествующего стирания, поскольку это может привести к снижению количества возможных циклов перезаписи и сокращению ресурса микросхемы.

Не рекомендуется производить сброс микросхемы во время операции программирования/стирания, поскольку это может привести к снижению количества возможных циклов перезаписи и сокращению ресурса микросхемы.

Порядок подачи и снятия напряжения питания и входных сигналов на микросхему:

- подача (включение микросхемы) общий, питание, сигнал SEL\_SPI, входные сигналы или одновременно;

- снятие (выключение микросхемы) в обратном порядке или одновременно.

## 5 Описание функционирования

## 5.1 Режим параллельного интерфейса

## 5.1.1 Поддерживаемые операции на шине памяти

В разделе описываются необходимые условия и операции, поддерживаемые микросхемой, которые инициируются через внутренний командный регистр. Командный регистр не занимает адресное пространство памяти. Командный регистр состоит из триггеров, которые хранят информацию, поступающую с шин адреса и данных, необходимую для выполнения команд. Содержимое регистра используется внутренней машиной состояний, которая формирует операции для микросхемы. Для управления микросхемой служит параллельная асинхронная шина, включающая все адреса, данные и сигналы управления (далее — шина микросхемы). В таблице 2 показаны операции на шине микросхемы, требуемые входные и выходные уровни сигналов. Описание операций приведено в следующих разделах.

Таблица 2 – Таблица истинности микросхемы. Операции на шине памяти

|            | Операция                               | nCE | nOE | $_{ m nWE}$ | A20 – A18 | A17 – A7      | A6   | A5-A2 | A1 | A0             | D0-D7                                           | OE_HV        | A9_HV |  |

|------------|----------------------------------------|-----|-----|-------------|-----------|---------------|------|-------|----|----------------|-------------------------------------------------|--------------|-------|--|

| Чте        | ние                                    | L   | L   | Н           |           | вход          | цной | адре  | ec |                | выходные<br>данные                              | L            | L     |  |

| Зап        | ись по nCE                             |     | Н   | L           |           | ВХОД          | (ной | адре  | ec |                | входные данные                                  | е данные L L |       |  |

| Зап        | ись по nWE                             | L   | Н   |             |           | входной адрес |      |       |    | входные данные | L                                               |              |       |  |

| Xpa        | нение                                  | Н   | Н   | X           | X         | X             | X    | X     | X  | X              | Z(X)                                            | L            | L     |  |

| Hea        | ктивное состояние                      | L   | Н   | Н           | X         | X             | X    | X     | X  | X              | Z                                               | L            | L     |  |

|            | ановка защиты<br>гора                  | L   | Н   | L           | SA        | X             | L    | X     | X  | X              | Z(X)                                            | н н          |       |  |

| Сня        | тие защиты сектора                     | L   | Н   | L           | SA        | X             | Н    | X     | X  | X              | Z(X)                                            | Н            | Н     |  |

| Autoselect | Верификация<br>защищенности<br>сектора | L   | L   | Н           | SA        | X             | X    | X     | Н  | L              | выходные<br>данные 01h —<br>защищен<br>выходные | L            | Н     |  |

| Autos      | _                                      |     |     |             |           |               |      |       |    |                | данные 00h –<br>не защищен                      |              |       |  |

|            | ID Производителя                       | L   | L   | Н           | X         | X             | X    | X     | L  | L              | 01h                                             | L            | Н     |  |

|            | ID Микросхемы                          | L   | L   | Н           | X         | X             | X    | X     | L  | Н              | C8h                                             | L            | Н     |  |

Примечание – Обозначения в таблице:

H – логическая «1» U<sub>IH</sub>;

L – логический «0»  $U_{IL}$ ;

- переход уровня сигнала из логического «0» в «1»;

SA – адрес сектора (см. таблицу 4);

X – любое значение на входе, логический «0» или логическая «1»;

Z – выход в состоянии Z;

Z(X) – выход в состоянии Z, подать любой сигнал: логический «0» или логическую «1»

Значения сигналов для работы по параллельному интерфейсу приведены в таблице 3.

| T. ~    | 2          | T. ~      |            | _         |          | 1 •         |          |

|---------|------------|-----------|------------|-----------|----------|-------------|----------|

| Таблица | <b>1</b> — | - Таблица | истинности | ппя выроп | a untenc | пеиса мик   | cnocxem  |

| таолица | 9          | таолица   | nerminoem  | дли высор | a mirope | perieu miri | tpoeztem |

| Интефрейс             | SEL_SPI | STROBE | MRST | TCK | nOE |

|-----------------------|---------|--------|------|-----|-----|

| Параллельный          | L       | L      | X    | X   | X   |

| SPI                   | Н       | L      | X    | X   | Н   |

| Последовательный      | L       | Н      | Н    | 7   | Н   |

| Запрещенное состояние | Н       | Н      | X    | X   | X   |

Примечание – Состояние сигнала TDI не влияет на выбор интерфейса

## 5.1.2 Требования, предъявляемые при чтении данных

Для чтения данных с выходов система должна подать на выводы nCE и nOE уровень логического «0». Вывод nCE регулирует мощность и разрешает обращение к микросхеме. Вывод nOE осуществляет управление выводом данных на контактные площадки. Вывод nWE должен оставаться в состоянии логической «1».

Внутренний интерфейс управления переходит в состояние чтения данных при включении питания. Это гарантирует, что случайное изменение содержимого памяти не произойдет при переходных процессах питания. Никаких команд в этом режиме не нужно, чтобы получить данные. Цикл чтения аналогичен стандартному микропроцессорному циклу, во время которого адрес выставляется на входы адреса, а данные выдаются на выходы данных. Микросхема остается доступной для чтения, пока содержимое командного регистра не изменится.

Для дополнительной информации см. подпункт 5.1.8.1 «Чтение массива данных».

#### 5.1.3 Команды записи и командные последовательности

Для записи команд или командных последовательностей, которые включают программирование данных в микросхему и стирание секторов памяти, система должна подать на выводы nCE и nWE уровень логического «0». Вывод nOE должен оставаться в состоянии логической «1». Не допускается переключение адреса, когда выводы nCE и nWE одновременно находятся в состоянии логического «0». После положительного фронта nCE или nWE, в зависимости от того, какое из событий произошло раньше, сигналы адреса и данных необходимо удерживать не менее 15 нс.

Режим «Unlock Bypass» (разблокирование обходного регистра) позволяет ускорить программирование. В этом режиме для программирования байта требуются только два цикла вместо четырех. В подпункте 5.1.8.4 «Командная последовательность программирования байта» подробно описываются оба режима записи: стандартный и «Unlock Bypass».

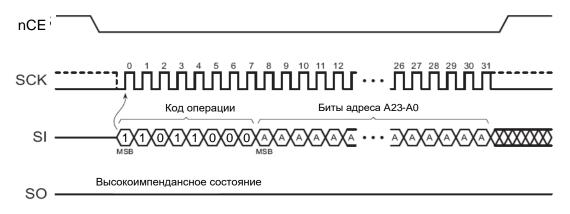

С помощью операции стирания можно стереть страницу, один сектор, несколько секторов или всю память. В таблице 4 приведено адресное пространство для каждого сектора. «Адрес сектора» состоит из адресных битов, позволяющих выбрать один из секторов. Стирание сектора и всей памяти подробно описано в пункте 5.1.8 «Описание команд».

После записи системой командной последовательности «Autoselect», (автоматический выбор) микросхема входит в режим «Autoselect». Система может прочитать Autoselect-коды из внутреннего регистра на выходы D0 – D7. Для этого применяются стандартные циклы чтения.

| Table the figure in the following the control of the first the control of the control of the first the control of th | Таблица | 4 – Адресное пространство секторов |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------|

|        |     |     |     | Диапазон адресов                           |  |  |  |  |

|--------|-----|-----|-----|--------------------------------------------|--|--|--|--|

| Сектор | A20 | A19 | A18 | (в шестнадцатеричной<br>системе счисления) |  |  |  |  |

|        |     |     |     |                                            |  |  |  |  |

| SA0    | 0   | 0   | 0   | 000000h-03FFFFh                            |  |  |  |  |

| SA1    | 0   | 0   | 1   | 040000h-07FFFh                             |  |  |  |  |

| SA2    | 0   | 1   | 0   | 080000h-0BFFFFh                            |  |  |  |  |

| SA3    | 0   | 1   | 1   | 0C0000h-0FFFFh                             |  |  |  |  |

| SA4    | 1   | 0   | 0   | 100000h-13FFFFh                            |  |  |  |  |

| SA5    | 1   | 0   | 1   | 140000h-17FFFFh                            |  |  |  |  |

| SA6    | 1   | 1   | 0   | 180000h-1BFFFFh                            |  |  |  |  |

| SA7    | 1   | 1   | 1   | 1C0000h-1FFFFFh                            |  |  |  |  |

## 5.1.4 Режим хранения

Если система не осуществляет операций чтения или записи в микросхему, то микросхема может находиться в режиме хранения. В режиме хранения ток потребления значительно понижается.

Для входа в режим хранения на вывод nCE необходимо подать напряжение  $U_{CC}\pm0.3$  B, более ограниченный диапазон, чем  $U_{IH}$ . Если  $U_{IH}\leq U_{nCE}< U_{CC}-0.3$  B, то микросхема будет находиться в режиме хранения, однако ток потребления будет больше. Выходы переходят в высокоимпедансное состояние независимо от состояния входа nOE. Ток потребления в режиме хранения зависит от напряжения на выводах D0-D7 и будет минимальным, если подать на них логическую «1» или логический «0».

Для перехода из режима хранения в режим чтения не требуется дополнительного времени.

Если микросхема не выбрана во время операций стирания или программирования, то она находится в режиме активного потребления, пока не закончится операция.

### **5.1.5** Режим «Autoselect»

Режим предоставляет идентификаторы производителя и микросхемы, а также обеспечивает верификацию защищенности секторов с помощью идентификационных кодов, выдаваемых по шине D0-D7. Режим «Autoselect» требует наличия напряжения  $U_{IH}$  на входе  $A9_HV$ . Адресные входы A1, A0 должны быть установлены в соответствии с таблицей 2. Адрес сектора должен выставляться на старших битах адреса в соответствии с таблицей 4.

Идентификаторы также могут быть получены через командный регистр, как приведено в таблицей 5. Этот метод не требует напряжения U<sub>IH</sub> на входе A9 HV.

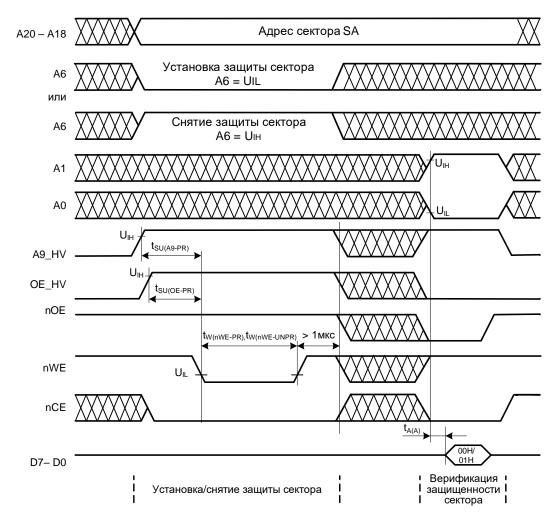

## 5.1.6 Установка и снятие защиты с сектора

Аппаратная защита сектора блокирует операции программирования и стирания для любого сектора.

Метод установки и снятия защиты с сектора требует напряжения  $U_{IH}$  на выводах A9 HV и OE HV.

Для установки защиты сектора необходимо установить напряжение  $U_{IH}$  на выводах  $A9\_HV$  и  $OE\_HV$ . Вывод nCE должен быть в активном состоянии (логический «0»). Адрес сектора, для которого необходимо установить защиту, должен быть установлен на адресных входах A18-A20 в соответствии с таблицей 4. На входе A6 должно быть установлено напряжение логического «0».

Процесс установки защиты сектора начинается по спаду сигнала nWE и заканчивается подъемом nWE через время  $t_{W(nWE-PR)}$ . Адрес сектора не должен меняться в течение этого времени. Алгоритм установки защиты сектора и связанные с ним временные диаграммы приведены на рисунке 35.

Для снятия защиты сектора необходимо установить напряжение  $U_{IH}$  на выводах  $A9\_HV$  и  $OE\_HV$ . Вывод nCE должен быть в активном состоянии (логический «0»). Адрес сектора, для которого необходимо снять защиту, должен быть установлен на адресных входах A18-A20 в соответствии с таблицей 4. На входе A6 должно быть установлено напряжение логической «1».

Процесс снятия защиты сектора начинается по спаду сигнала nWE и заканчивается подъемом nWE через время  $t_{W(nWE-UNPR)}$ . Адрес сектора не должен меняться в течение этого времени. Алгоритм установки защиты сектора и связанные с ним временные диаграммы приведены на рисунке 35.

Микросхема поставляется с незащищенными секторами. По желанию пользователя данные в микросхеме могут быть запрограммированы и установлены в защищенное состояние.

Для снижения тока потребления при операциях установки и снятия защиты сектора рекомендуется подать на выводы D0 - D7 логический «0» или логическую «1».

### 5.1.7 Аппаратная защита данных

Командные последовательности программирования или стирания включают в себя циклы разблокировки для защиты данных от ошибочной записи. В дополнение к этому нижеописанные методы аппаратной защиты предотвращают случайную запись или стирание, которые могут быть следствием переходных процессов при подаче и снятии питания, а также шумов системы.

В микросхему включена схема сброса при включении питания (power—on reset), которая обеспечивает блокирование внутренних схем программирования и стирания, а также командного регистра после подачи напряжения питания  $U_{CC}$  на время  $t_{SU(Ucc-nCEL)}$ . Значение времени  $t_{SU(Ucc-nCEL)}$  приведено в таблице 15.

На входах nCE, nOE, nWE установлены фильтры импульсных помех длительностью менее 5 нс (типичное значение) для предотвращения случайных циклов записи.

Если  $U_{nWE} = U_{IICE} = U_{II}$  и  $U_{nOE} = U_{IH}$  при включении питания, микросхема не воспримет команду по положительному фронту nWE. Внутренний интерфейс управления автоматически переходит в режим чтения данных при включении питания.

## 5.1.8 Описание команд

Запись командных последовательностей в командный регистр инициирует операции микросхемы. В таблице 5 приведены доступные командные последовательности. Запись некорректного адреса или данных, или их запись в неправильной последовательности может перевести микросхему в неизвестное состояние. Чтобы вернуть микросхему в состояние чтения массива данных требуется выполнить команду сброса «Reset».

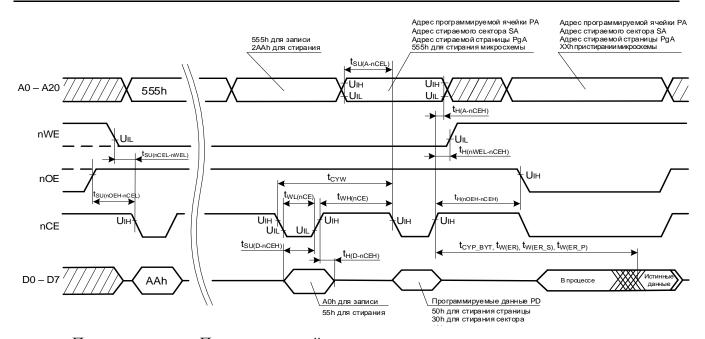

Все адреса и данные защелкиваются по фронту nWE или nCE, в зависимости от того, какое из событий произойдет раньше. Соответствующие временные диаграммы приведены на рисунках 31-40.

Таблица 5 – Определение команд на шине микросхемы

|            | Y.                           | 19    |         |      |         |      | Ц    | иклы | на ши | не    |      |      |           |      |  |  |

|------------|------------------------------|-------|---------|------|---------|------|------|------|-------|-------|------|------|-----------|------|--|--|

| пос        | Командные<br>ледовательности | Циклы | Пер     | вый  | Вто     | рой  | Tpe  | тий  | Четве | ертый | ПяП  | гый  | Шес       | стой |  |  |

|            | лодовательности              | П     | Addr    | Data | Addr    | Data | Addr | Data | Addr  | Data  | Addr | Data | 555<br>SA | Data |  |  |

| Read       |                              | 1     | RA      | RD   |         |      |      |      |       |       |      |      |           |      |  |  |

| Reset      |                              | 1     | XX<br>X | F0   |         |      |      |      |       |       |      |      |           |      |  |  |

| Ente       | er Autoselect                | 3     | 555     | AA   | 2AA     | 55   | 555  | 90   |       |       |      |      |           |      |  |  |

| ct         | ID<br>Производителя          | 1     | X00     | 01   |         |      |      |      |       |       |      |      |           |      |  |  |

| sele       | ID Устройства                | 1     | X01     | C8h  |         |      |      |      |       |       |      |      |           |      |  |  |

| Autoselect | Верификация                  |       | (SA)    | 00   |         |      |      |      |       |       |      |      |           |      |  |  |

| A          | защищенности сектора         | 1     | I       | 1    | X02     | 01   |      |      |       |       |      |      |           |      |  |  |

| Prog       | gram                         | 4     | 555     | AA   | 2AA     | 55   | 555  | A0   | PA    | PD    |      |      |           |      |  |  |

| Ente       | er Unlock Bypass             | 3     | 555     | AA   | 2AA     | 55   | 555  | 20   |       |       |      |      |           |      |  |  |

| Unlock     | Program Reset                | 2     | XX<br>X | A0   | PA      | PD   |      |      |       |       |      |      |           |      |  |  |

| Unl        | Reset                        | 2     | XX<br>X | 90   | XX<br>X | 00   |      |      |       |       |      |      |           |      |  |  |

| Chi        | p Erase                      | 6     | 555     | AA   | 2AA     | 55   | 555  | 80   | 555   | AA    | 2AA  | 55   | 555       | 10   |  |  |

| Sect       | tor Erase                    | 6     | 555     | AA   | 2AA     | 55   | 555  | 80   | 555   | AA    | 2AA  | 55   | SA        | 30   |  |  |

| Page       | e Erase                      | 6     | 555     | AA   | 2AA     | 55   | 555  | 80   | 555   | AA    | 2AA  | 55   | PgA       | 50   |  |  |

## Примечания

1 Обозначения в таблице:

X – значение  $U_{IL}$  или  $U_{IH}$ ;

RA – адрес читаемой ячейки памяти;

RD – данные читаемые по адресу RA во время операции чтения;

- PA адрес программируемой ячейки памяти (адрес защелкивается по фронту nWE или nCE);

- PD данные, программируемые в ячейку памяти PA (данные защелкиваются по фронту nWE или nCE);

- SA адрес сектора, который верифицируется (в режиме «Autoselect») или стирается. Сектор выбирается с помощью адресных битов A20 A18.

- PgA адрес страницы, которая стирается. С помощью адресных битов A20 A11 выбирается страница.

- 2 Описание операций на шине устройства приведено в таблице 2.

- 3 Все значения приведены в шестнадцатеричной системе.

- 4 Во всех командных последовательностях, за исключением последовательностей «Read», «Autoselect ID Производителя», «Autoselect ID Устройства», «Autoselect Верификация защищенности сектора», проводятся операции записи.

- 5 Адресные биты A20-A12 не имеют значения для командных последовательностей и последовательностей «Unlock Bypass».

- 6 Во время операции чтения командные последовательности и последовательности «Unlock Bypass» не требуются.

- 7 Команда «Reset» требуется для возврата в режим чтения массива данных, если микросхема находится в режиме «Autoselect» или статусный бит D5 установлен в логическую «1» (пока устройство выдает данные статуса).

- 8 Команду «Enter Autoselect» требуется выполнить перед подачей команд «Autoselect ID Производителя», «Autoselect ID Устройства», «Autoselect Верификация защищенности сектора».

- 9 При верификации защищенности сектора читаются данные:

- 00h для незащищенного сектора;

- 01h для защищенного сектора.

- 10 Команду «Unlock Bypass» требуется выполнить перед командной «Unlock Bypass Program».

- 11 Требуется команда «Unlock Bypass Reset» для возврата в режим чтения массива данных, если микросхема находилось в режиме «Unlock Bypass»

#### 5.1.8.1 Чтение массива данных

Микросхема автоматически устанавливается в режим чтения данных после включения питания. Микросхема также готова к чтению массива данных после завершения алгоритма программирования или стирания.

Если статусный бит D5 установлен в логическую «1» или микросхема находится в режиме «Autoselect», для перевода микросхемы в режим чтения массива данных должна быть подана команда сброса «Reset». Описание команды «Reset» приведено в подпункте 5.1.8.2.

Для получения дополнительной информации см. пункт 5.3.2 «Операция чтения массива данных».

## 5.1.8.2 Команда сброса «Reset»

Запись команды «Reset» переводит микросхему в режим чтения массива данных. Адресные биты не имеют значения для этой команды.

Команда «Reset» может быть записана между циклами командной последовательности стирания до того, как начнется стирание. Микросхема перейдет в режим чтения данных. Если стирание началось, команда сброса игнорируется до окончания операции стирания.

Команда «Reset» может быть записана между циклами командной последовательности программирования до того, как начнется программирование. Это сбросит микросхему в режим чтения данных. Если программирование началось, то микросхема игнорирует команду сброса, пока не закончится операция.

Команда «Reset» может быть записана между циклами командной последовательности «Autoselect». Для возврата из режима «Autoselect» в режим чтения массива данных необходимо записать команду «Reset».

Если статусный бит D5 установился в «1» во время операции программирования или стирания, то записью команды «Reset» микросхема возвращается в режим чтения массива данных.

## 5.1.8.3 Команда режима «Autoselect»

Командная последовательность режима «Autoselect» позволяет хост-системе определить производителя микросхемы и его код, а также получить информацию о защищенных секторах. В таблице 5 приведены необходимые циклы для входа в этот режим. Этот метод альтернативный методу, приведенному в таблице 2, который требует напряжения  $U_{IH}$  на выводе  $A9\_HV$ .

Вход в режим «Autoselect» осуществляется командной последовательностью «Enter Autoselect», состоящей из трех циклов записи. После этого система может читать любой адрес в любое время без инициализации других командных последовательностей. Цикл чтения по адресу 00h возвращает код производителя. Цикл чтения по адресу 01h возвращает код микросхемы. Цикл чтения, содержащий адрес сектора (SA) и адрес 02h возвращает 01h, если сектор защищен, или 00h, если не защищен. Для определения необходимого адреса сектора смотрите таблицу 4.

Система может записать команду «Reset» и выйти из режима «Autoselect» в режим чтения массива данных.

## 5.1.8.4 Командная последовательность программирования байта

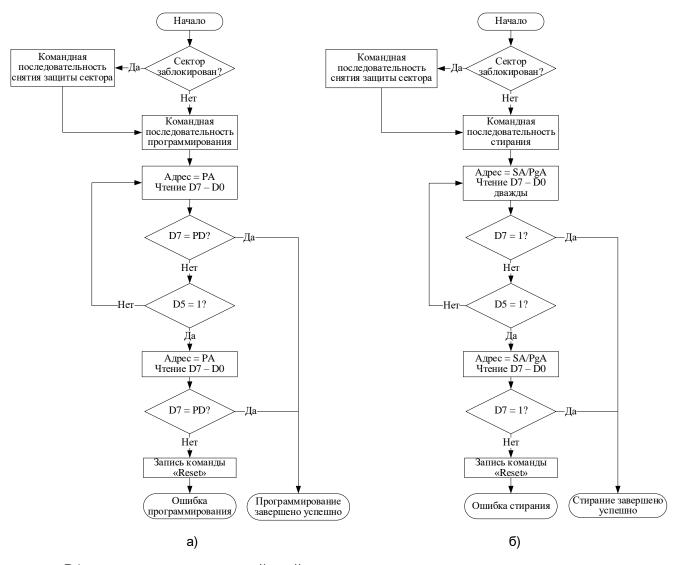

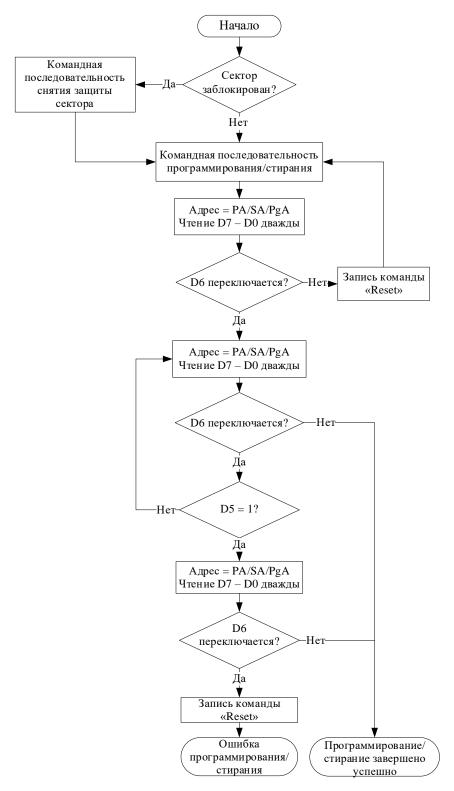

Командная последовательность программирования байта программирует один байт в микросхему. Операция программирования инициируется четырьмя циклами на шине микросхемы. Программная последовательность состоит из двух циклов разблокирования, команды «Setup», адреса и программируемых данных, запись которых инициирует внутренний алгоритм программирования. Дальнейший контроль времени программирования производить не требуется, так как это осуществляется логикой микросхемы. Микросхема автоматически обеспечивает внутреннюю генерацию программных импульсов. В таблице 5 приведены необходимые циклы для входа в этот режим. Алгоритмы программирования микросхемы приведены на рисунках 3 – 5. После подачи командной последовательности программирования байта необходима проверка наличия статуса операции программирования. Статус операции программирования проверяется путем опроса статусных бит D7 или D6. Более подробная информация об

этих статусных битах приведена в пункте 5.1.9 «Статус операции программирования / стирания». В случае отсутствия статуса операции программирования, необходимо осуществить сброс микросхемы и повторить командную последовательность программирования байта.

РА – адрес программируемой ячейки памяти;

PD – данные, программируемые в ячейку памяти PA;

SA – адрес стираемого сектора;

PgA – адрес стираемой страницы.

Рисунок 3 — Алгоритм процедуры программирования/стирания без отслеживания статуса операции

Допускается не проводить проверку статуса операции программирования. В этом случае необходимо после подачи командной последовательности программирования байта выдержать паузу не менее минимального времени программирования байта t<sub>СУР\_ВУТ</sub>, после чего осуществить проверку записи данных путем чтения запрограммированного адреса. В зависимости от содержимого ячейки возможны следующие дальнейшие действия:

- содержимое ячейки соответствует записываемой информации. Необходимо перейти к записи следующего адреса или закончить процедуру программирования;

- ячейка оказалась незапрограммированной (содержимое равно FFh). Необходимо выполнить сброс микросхемы и повторить операцию программирования байта;

- ячейка содержит информацию несоответствующую записываемой, необходимо осуществить сброс микросхемы, затем произвести процедуру стирания сектора или всего накопителя памяти. Только после этого возможно вернуться к программированию данного адреса.

После завершения внутреннего алгоритма программирования микросхема возвращается в режим чтения массива данных и адрес больше не защелкивается.

Любая команда, записанная в течение внутреннего алгоритма программирования, игнорируется.

Программирование может осуществляться в любой последовательности, в любой сектор, по любому адресу. Биты не могут быть запрограммированы обратно из «0» в «1». Попытка сделать это может прекратить операцию и установить бит D5 в «1 Только операция стирания может конвертировать биты из «0» в «1».

**Внимание!** Запрещается производить запись по одному и тому же адресу более одного раза без предшествующего стирания, поскольку это может привести к снижению количества возможных циклов перезаписи и сокращению ресурса микросхемы.

**Внимание!** Не рекомендуется производить сброс питания во время операции программирования, поскольку это может привести к снижению количества возможных циклов перезаписи и сокращению ресурса микросхемы.

## 5.1.8.5 Командная последовательность режима «Unlock Bypass»

Режим «Unlock Bypass» позволяет системе программировать байты быстрее, чем при использовании стандартных последовательностей программирования. Режим «Unlock Bypass» инициируется с помощью двух циклов разблокирования и цикла разблокирования команды «Bypass», 20h. После входа в режим достаточно командной последовательности из двух циклов для программирования байта. Первый цикл этой последовательности содержит команду «Unlock Bypass Program», A0h. Второй цикл содержит адрес и программируемые данные. Последующие данные программируются подобным методом за два цикла. Этот метод обходится без двух циклов разблокирования, необходимых в стандартной последовательности программирования. В результате общее время программирования уменьшится. В таблице 5 приведены необходимые циклы для входа в этот режим.

В режиме «Unlock Bypass» разрешены только команды «Unlock Bypass Program» (программирование при разблокированном обходном регистре) и «Unlock Bypass Reset» (сброс при разблокированном обходном регистре). Для выхода из режима «Unlock Bypass» системе необходимо выдать командную последовательность «Unlock Bypass Reset», состоящую из двух циклов. Первый цикл должен содержать данные 90h, второй цикл данные 00h. После этого микросхема возвращается в режим чтения массива данных.

Алгоритм процедуры программирования показан на рисунках 3 - 5.

#### 5.1.8.6 Командная последовательность стирания страницы

Командная последовательность стирания страницы состоит из шести циклов на шине памяти: двух циклов разблокирования, команды «Setup», двух дополнительных циклов разблокирования, адреса стираемой страницы и команды «Page Erase», которая запускает внутренний алгоритм стирания. При подаче адреса стираемой страницы в шестом цикле командной последовательности младшие биты A10 — A0 обязательно должно быть равны 000h. Микросхеме не требуется предварительное программирование перед стиранием. Дополнительно контролировать временные характеристики

микросхемы после запуска внутреннего алгоритма стирания не требуется. В таблице 5 приведены необходимые циклы для входа в этот режим.

Любая команда, записанная в память микросхемы во время работы внутреннего алгоритма стирания, игнорируется.

При необходимости можно определить статус операции стирания с помощью бита статуса D7, D6 или D2. Более подробная информация об этих статусных битах приведена в пункте 5.1.9 «Статус операции программирования / стирания».

После завершения внутреннего алгоритма стирания микросхема возвращается в режим чтения массива данных, и адрес больше не защелкивается.

Алгоритм процедуры стирания приведен на рисунках 3 - 5.

**Внимание!** Не рекомендуется производить сброс питания во время операции стирания, поскольку это может привести к снижению количества возможных циклов перезаписи и сокращению ресурса микросхемы.

## 5.1.8.7 Командная последовательность стирания микросхемы

Командная последовательность стирания микросхемы состоит из шести циклов на шине микросхемы: двух циклов разблокирования, команды «Setup», двух дополнительных циклов разблокирования и команды «Chip Erase», которая запускает внутренний алгоритм стирания. Микросхеме не требуется предварительное программирование перед стиранием. Не требуется дополнительно контролировать временные характеристики микросхемы после запуска внутреннего алгоритма стирания. В таблице 5 приведены необходимые циклы для входа в этот режим.

Любая команда, записанная во время работы внутреннего алгоритма стирания, игнорируется.

При необходимости можно определить статус операции стирания с помощью бит статуса D7, D6 или D2. Более подробная информация об этих статусных битах приведена в пункте 5.1.9 «Статус операции программирования / стирания». После завершения внутреннего алгоритма стирания микросхема возвращается в режим чтения массива данных, и адрес больше не защелкивается.

Алгоритм процедуры стирания показан на рисунках 3 - 5.

**Внимание!** Не рекомендуется производить сброс питания во время операции стирания, поскольку это может привести к снижению количества возможных циклов перезаписи и сокращению ресурса микросхемы.

## 5.1.8.8 Командная последовательность стирания сектора

Командная последовательность стирания сектора состоит из шести циклов на шине микросхемы: двух циклов разблокирования, команды «Setup», двух дополнительных циклов разблокирования, адреса стираемого сектора и команды «Sector Erase». В таблице 5 приведены необходимые циклы для входа в этот режим.

Микросхеме не требуется предварительное программирование перед стиранием. Не требуется дополнительно контролировать временные характеристики микросхемы после запуска внутреннего алгоритма стирания.

После записи командной последовательности стирания сектора начинается отсчет времени ожидания не менее 50 мкс. В течение времени ожидания могут быть записаны

дополнительные командные последовательности «Sector Erase» для других секторов. Загрузка буфера стираемых секторов может происходить в любой последовательности и количество секторов может быть от одного до восьми.

Время между этими дополнительными командными последовательностями должно быть менее 50 мкс, иначе последние адрес и команда не будут приняты, так как начнется стирание. Если время между дополнительными командами «Sector Erase» менее 50 мкс, системе не требуется отслеживать статусный бит D3. Любые команды, за исключением «Sector erase», в течение времени ожидания сбрасывают микросхему в режим чтения массива данных. В таком случае необходимо повторно подать командную последовательность и дополнительные адреса секторов.

Система может отслеживать статусный бит D3, чтобы определить окончание времени ожидания 50 мкс. Время ожидания начинается от последнего положительного фронта nWE в командной последовательности.

После завершения внутреннего алгоритма стирания микросхема возвращается в режим чтения массива данных и адрес больше не защелкивается. Статус операции стирания определяется с помощью битов статуса D7, D6 или D2. Более подробная информация об этих статусных битах приведена в пункте 5.1.9 «Статус операции программирования / стирания».

Алгоритм процедуры стирания показан на рисунках 3 - 5.

**Внимание!** Не рекомендуется производить сброс питания во время операции стирания, поскольку это может привести к снижению количества возможных циклов перезаписи и сокращению ресурса микросхемы.

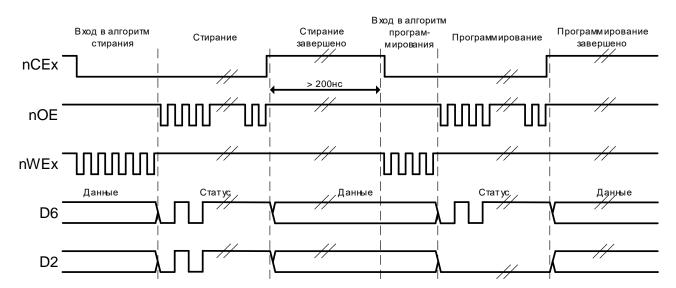

## 5.1.9 Статус операции программирования / стирания

Микросхема выдает несколько битов для определения статуса операций программирования/стирания: D2, D3, D5, D6 и D7. В таблице 6 и следующих подразделах описываются функции этих битов. С помощью битов D6 и D7 предлагаются методы определения статуса операций программирования и стирания.

| •                | J 1         |               |    |     |                  |

|------------------|-------------|---------------|----|-----|------------------|

| Операция         | D7          | D6            | D5 | D3  | D2               |

| Программирование | Инверсия D7 | Переключается | 0  | нет | Не переключается |

| Стирание         | 0           | Переключается | 0  | 1   | Переключается    |

Таблица 6 – Биты статуса микросхемы

## 5.1.9.1 Опрашиваемый бит D7

Опрашиваемый бит D7 показывает хост системе статус выполнения внутреннего алгоритма (в прогрессе или завершен). Опрос этого бита правомерен после последнего фронта на nWE в командной последовательности программирования или стирания.

Во время выполнения внутреннего алгоритма программирования на D7 выводится значение, инверсное по отношению к программируемым данным. После завершения внутреннего алгоритма программирования микросхема выводит на этот вывод программируемые данные. Система должна выдавать правильный адрес программирования, чтобы прочитать информацию о статусном бите. Если адрес

программирования находится в диапазоне защищенного сектора, бит статуса выводится на D7 на время не более 2 мкс, а затем микросхема возвращается в режим чтения массива данных.

Во время выполнения внутреннего алгоритма стирания на D7 выводится значение «0». Когда внутренний алгоритм стирания завершен, на D7 выводится «1». Аналогично инверсному выводу данных, описанному в алгоритме программирования данных. Функция стирания меняет все биты в секторе на «1», поэтому перед этим микросхема выводит инверсные по отношению к «1» данные, или «0». Система должна выдавать адрес внутри любого сектора из выбранных для стирания, чтобы прочитать правильную статусную информацию на D7.

После того, как записана командная последовательность стирания и все сектора защищены от стирания, бит статуса выводится на D7 на время не более 90 мкс, а затем микросхема возвращается в режим чтения массива данных. Если не все сектора защищены, то во время выполнения внутреннего алгоритма стираются все незащищенные сектора и игнорируются выбранные для стирания защищенные.

Если система определяет смену на D7 с инверсного на правильный, это означает, что данные на D7 – D0 правильные. Данные D7 – D0 могут меняться асинхронно, если nOE и nCE установлены в «0».

Состояния выхода D7 в различных режимах приведены в таблице 6. Алгоритмы процедур программирования и стирания с отслеживанием бита статуса операции D7 приведена на рисунке 4.

РА – адрес программируемой ячейки памяти;

PD – данные, программируемые в ячейку памяти PA;

SA – адрес стираемого сектора;

PgA – адрес стираемой страницы.

Рисунок 4 — Алгоритмы процедур программирования (а) и стирания (б) с отслеживанием битов статуса операции D5 и D7

## 5.1.9.2 Переключающийся бит 1 на D6

Переключающийся бит 1 на D6 показывает статус внутреннего алгоритма стирания или записи. Этот бит может быть прочитан по любому адресу и правомерен после последнего фронта сигнала nWE в командной последовательности (перед операцией программирования или стирания) и во время паузы ожидания при стирании сектора.

Во время внутреннего алгоритма программирования или стирания цикл чтения по любому адресу изменяет значение статусного бита D6 на инверсное. Система может использовать любой из сигналов nCE или nOE для управления циклами чтения. По завершении операции переключения на D6 останавливаются.

Если записана командная последовательность стирания и все выбранные для стирания сектора защищены, D6 переключается не более 90 мкс, а затем микросхема переходит в режим чтения массива данных. Если не все выбранные для стирания сектора

защищены, то во время выполнения внутреннего алгоритма стирания незащищенные сектора стираются, а защищенные игнорируются.

Если микросхема стирает сектор (выполняется внутренний алгоритм стирания), D6 переключается. В качестве альтернативы можно использовать бит D7 (см. подпункт 5.1.9.1 «Опрашиваемый бит D7»).

Если адрес программируемой ячейки находится в диапазоне защищенного сектора, D6 переключается не более 2 мкс после записи командной последовательности программирования, а затем микросхема возвращается в режим чтения массива данных.

Состояния выхода D6 в различных режимах приведены в таблице 6. Алгоритм процедур программирования и стирания с отслеживанием бита статуса операции D6 приведена на рисунке 5.

РА – адрес программируемой ячейки памяти;

SA – адрес стираемого сектора;

PgA – адрес стираемой страницы.

Рисунок 5 — Алгоритм процедуры программирования/стирания с отслеживанием битов статуса операции D5 и D6

## 5.1.9.3 Переключающийся бит 2 на D2

Переключающийся бит 2 на D2 совместно с D6 используется для определения, выполняется или нет внутренний алгоритм стирания. Этот бит правомерен только после последнего фронта сигнала nWE в командной последовательности. Во время внутреннего

алгоритма стирания цикл чтения по любому адресу изменяет значение статусного бита D2 на инверсное. Система может использовать сигналы nOE или nCE для управления циклами чтения. По завершении операции стирания переключения на D2 останавливаются.

Дополнительная информация о различиях этих бит приведена в таблице 6. Алгоритмы процедур программирования и стирания с отслеживанием битов статуса операции приведены на рисунках 4, 5. Различие между статусными битами D2 и D6 приведено на рисунке 36.

## 5.1.9.4 Чтение переключающихся бит D6/D2

При чтении переключающихся бит статуса, система должна прочитать D7–D0 дважды, чтобы определить, изменяется бит статуса или нет. Обычно после первого чтения система сохраняет значение переключающегося бита. После второго чтения система сравнивает новое значение статусного бита с первым прочитанным. Если статусный бит не меняется, система завершила операцию программирования или стирания. Система может прочитать данные с D7–D0 на следующем цикле чтения.

Если после двух циклов чтения система определила, что статусный бит изменяется, системе необходимо прочитать значение бита D5. Если этот бит установлен в «1», системе необходимо еще раз определить переключается статусный бит или нет, так как переключения могли завершиться. Если бит статуса больше не переключается, операция стирания или программирования успешно завершена. Если переключающийся бит все еще изменяется, операция не была успешно завершена и система должна записать команду сброса для возврата в режим чтения массива данных.

По похожему алгоритму система должна продолжать опрос и отслеживание переключающегося бита, если D2 или D6 переключаются и D5 не установлен в «1». В качестве альтернативы система может выполнять другие свои задачи, а по их завершении определить статус операции.

### 5.1.9.5 Бит превышения времени операции D5

Бит D5 позволяет определить, превысила ли операция программирования или стирания отведенный для нее интервал времени. При превышении отведенного на операцию времени бит D5 устанавливается в «1». Эта ошибочная ситуация показывает, что операция программирования или стирания не была завершена успешно.

Такая ошибка может возникать, если система попытается запрограммировать «единицы» в ячейку, где ранее были запрограммированы «нули». Только операция стирания может изменить содержимое ячейки из «0» в «1». При таких условиях микросхема останавливает операцию и, когда время операции превысит допустимое, устанавливается бит D5 в «1».

При возникновении таких ситуаций система должна выдать команду сброса, чтобы перевести микросхему в режим чтения массива данных.

## 5.1.9.6 Таймер паузы при стирании сектора D3

После записи командной последовательности стирания сектора система может прочитать бит D3, чтобы определить, началась операция стирания или нет (этот бит не применим при стирании страницы и всей микросхемы). Если выбираются

дополнительные сектора для стирания, время ожидания повторяется после каждой дополнительной команды стирания сектора. Когда время ожидания завершено, бит D3 переключается из «0» в «1». Если время между дополнительными командами стирания сектора меньше 50 мкс, система может не отслеживать состояние бита D3.

После того, как система записала командную последовательность стирания сектора, необходимо прочитать состояние статусных бит D7 или D6, чтобы определить приняла ли микросхема команду, а затем читать D3. Если D3 в «1», то внутренний цикл программирования начался. Пока операция стирания не завершится другие команды игнорируются. Если D3 в «0», микросхема может принимать дополнительные команды стирания сектора. Чтобы быть уверенным, что команда принята, система должна проверять состояние D3 перед каждой следующей командной последовательностью стирания сектора. Если при повторной проверке D3 в «1», последняя командная последовательность может быть не принята. Состояния выхода D3 в различных режимах приведены в таблице 6.

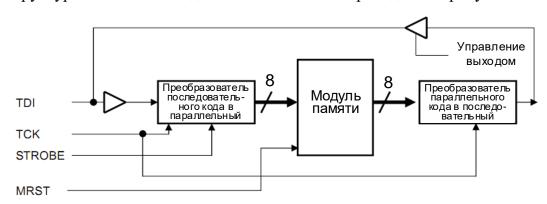

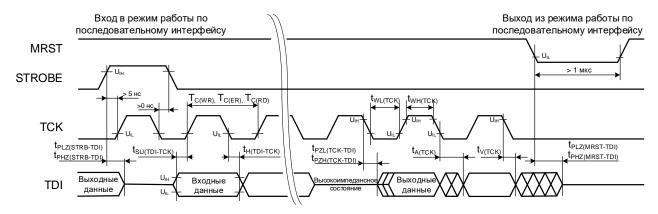

## 5.2 Режим последовательного интерфейса FLASH

Структурная схема последовательного канала приведена на рисунке 6.

Примечание — Значения сигналов для работы в последовательном режиме см. в таблице 3.

Рисунок 6 – Структурная схема последовательного канала

Для входа в последовательный режим работы STROBE = 1 должен быть зафиксирован по переднему фронту TCK при MRST = 1. Для выхода из последовательного режима необходимо произвести сброс с помощью сигнала MRST = 0. В последовательном режиме работы сигнал  $SEL\_SPI = 0$ . Значения сигналов для работы по последовательному интерфейсу см. в таблице 3.

Через последовательный интерфейс возможно выполнение следующих операций: стирания, программирования и чтения. Операции стирания могут быть выполнены одновременно над всем блоком объемом 2 Мбит. Операции программирования и чтения памяти могут выполняться непосредственно с каждой 8-разрядной или 16-разрядной ячейкой памяти (разрядность памяти выбирается в команде). При стирании ячейки памяти принимают значение, равное «1». При выполнении операции программирования производится запись «0». Через последовательный интерфейс доступна для стирания, программирования и чтения дополнительная область памяти информационной емкостью 16 Кбит в каждом из восьми блоков.

Для инициирования стирания или программирования необходимо передать командные последовательности (см. таблицу 7), состоящие из нескольких циклов.

Из режима последовательного интерфейса микросхема может быть переведена в режим хранения. В режиме хранения ток потребления значительно понижается.

Для входа в режим хранения необходимо подать на вывод MRST напряжение не более 0,3 B, а на вывод nCE напряжение  $U_{CC} \pm 0,3$  B. Это более ограниченные диапазоны, чем  $U_{IL}$  и  $U_{IH}$ . Если 0,3 B <  $U_{MRST} \leq U_{IL}$  или  $U_{IH} \leq U_{nCE} < U_{CC} - 0,3$  B, то микросхема будет находиться в режиме хранения, однако ток потребления будет больше.

#### 5.2.1 Командные последовательности

Командные последовательности программирования/стирания приведены в таблице 7.

| Таблица 7 – Командные последовательное |

|----------------------------------------|

|----------------------------------------|

| Командные           | 19    |      |         |      |      | I      | [иклы і | на шин    | e    |       |      |        |     |

|---------------------|-------|------|---------|------|------|--------|---------|-----------|------|-------|------|--------|-----|

| последова-          | Циклы | Пер  | рвый Вт |      | рой  | Третий |         | Четвертый |      | Пятый |      | Шестой |     |

| тельности           | П     | Addr | Data    | Addr | Data | Addr   | Data    | Addr      | Data | Addr  | Data | Addr   | Dat |

| Program             | 4     | 555  | AA      | AAA  | 55   | 555    | A0      | PA        | PD   |       |      |        |     |

| Main block<br>Erase | 6     | 555  | AA      | AAA  | 55   | 555    | 80      | 555       | AA   | AAA   | 55   | 555    | 10  |

| NVR block<br>Erase  | 6     | 555  | AA      | AAA  | 55   | 555    | 80      | 555       | AA   | AAA   | 55   | 000    | 50  |

$\Pi$ римечание — PD — данные, программируемые в ячейку памяти PA

Командная последовательность «Main block Erase» предназначена для стирания одного из восьми блоков памяти информационной емкостью 2 Мбит. Командная последовательность «NVR block Erase» предназначена для стирания дополнительной области памяти информационной емкостью 16 Кбит в одном из восьми блоков памяти.

В таблице 8 описаны стартовые символы режимов работы последовательного интерфейса.

Таблица 8 – Стартовые символы режимов работы последовательного интерфейса

| 1-ый символ | 2-ой символ | Режим работы   |  |  |  |

|-------------|-------------|----------------|--|--|--|

| 0           | 0           | Полный цикл    |  |  |  |

| 0           | 1           | Командный цикл |  |  |  |

| 1           | 0           | Цикл чтения    |  |  |  |

| 1           | 1           | Повтор цикла   |  |  |  |

#### 5.2.1.1 Режим полного цикла

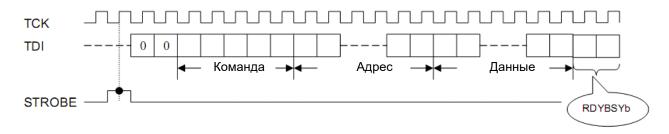

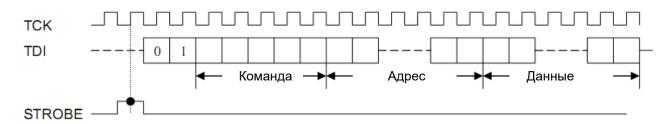

Временная диаграмма режима полного цикла приведена на рисунке 7.

Рисунок 7 – Режим полного цикла

Данный цикл может быть только четвертым при программировании данных или шестым при стирании памяти.

Данный инициализируется стартовым 00. режим символом далее последовательно передаются адрес программируемой ячейки памяти или адрес стирания и программируемые данные или соответствующий код стирания (10h или 50h). После этого вывод TDI переключается на выход и на него выводится состояние бита RDYBSYb (занятости). В случае инициирования внутреннего алгоритма программирования или стирания этот сигнал сначала переключается в «0», а по завершении операции переключается в «1». Синхросигнал ТСК необходимо подавать постоянно до окончания операции (для режима программирования TCK подается с периодом  $T_{C(WR)}$ , для режима стирания с периодом  $T_{C(ER)}$ ). Для гарантированного считывания состояния бита RDYBSYb необходимо производить не менее четырех последовательных выборок с объединением результата по «И».

**Внимание!** До завершения операции программирования или стирания (RDYBSYb=0) запрещено подавать режим полного цикла, поскольку это может привести к потере информации и сокращению ресурса микросхемы.

**Внимание!** Запрещается производить сброс последовательного интерфейса с помощью сигнала MRST=0 до завершения операций программирование/стирание, поскольку это может привести к снижению количества возможных циклов перезаписи и сокращению ресурса микросхемы.

Команды, адрес и данные передаются младшими разрядами вперед. В случае 8-разрядных данных адрес передается 17-разрядный, а в случае 16-разрядных данных адрес передается 16-разрядный. Данные также передаются соответственно 8- или 16-разрядные. В случае записи 16-разрядных данных младший байт берется из таблицы 7, а старший байт имеет нулевое значение.

Далее приведена структура команды.

| MSB  |      |      |      |     |      |     |     |      |       | LSB   |

|------|------|------|------|-----|------|-----|-----|------|-------|-------|

| Num3 | Num2 | Num1 | Num0 | CEB | NVRB | OEB | WEB | TMEN | BYTEB | VREAD |

Рисунок 8 – Структура команды

Num3-Num1 — биты для выбора одного из 8 блоков памяти информационной емкостью 2 Мбит при операциях программирования/ стирания/чтения;

Num0 – бит для выбора подблока памяти информационной емкостью 1 Мбит при операциях программирования/чтения. При операциях стирания не учитывается;

CEB – бит разрешения доступа к области памяти, выбранной с помощью Num3-Num0 (активный уровень логический «0»);

NVRB — бит разрешения доступа к дополнительной области памяти блока информационной емкостью 16 Кбит, выбранной с помощью Num3-Num1 (активный уровень логический «0»);

OEB – бит разрешения чтения данных (активный уровень логический «0»);

WEB — бит разрешения программирования/стирания памяти (активный уровень логический (0));

TMEN – бит должен быть в нуле;

BYTEB — бит выбирает разрядность внутренней шины данных: 1-16 разрядов, 0-8 разрядов;

VREAD – бит должен быть в нуле.

Память состоит из восьми блоков (состоят из двух подблоков) размером по 2 Мбит. Каждый блок выбирается комбинацией битов Num3-Num1 как описано выше. Каждый подблок в составе блока выбирается с помощью бита Num0.

#### 5.2.1.2 Режим командного цикла

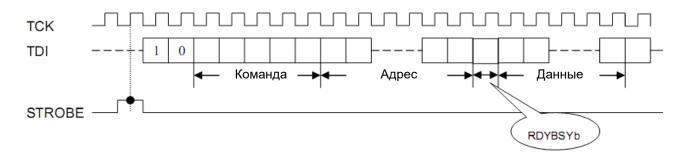

Временная диаграмма режима командного цикла приведена на рисунке 9.

Рисунок 9 – Режим командного цикла

Данный цикл может быть только первым, вторым, третьим при программировании данных и любым при стирании данных.

Данный режим инициируется стартовым символом 01 так же, как и в полном цикле, затем следует команда, адрес и данные. Отличие состоит в том, что в этом режиме адрес фиксирован и всегда 12-разрядный. Данные также фиксированы и всегда 8-разрядные. Для выполнения цикла, после его передачи необходимо подать не менее трех дополнительных импульсов ТСК.

**Внимание!** До завершения операции программирования или стирания (RDYBSYb=0) запрещено подавать режим командного цикла, поскольку это может привести к потере информации и сокращению ресурса микросхемы.

## 5.2.1.3 Режим цикла чтения

Временная диаграмма режима цикла чтения приведена на рисунке 10.

Рисунок 10 – Режим цикла чтения

Данный режим инициируется стартовым символом 10, далее последовательно через вывод TDI передаются команда и адрес, затем вывод TDI переключается на выход и выводится состояние бита занятости RDYBSYb. Если RDYBSYb в «1», далее младшими разрядами вперед выдвигаются данные соответствующей разрядности. Адрес 17-разрядный для 8-разрядного режима данных и 16-разрядный для 16-разрядного режима данных.

**Внимание!** До завершения операции программирования или стирания (RDYBSYb=0) запрещено подавать режим цикла чтения, поскольку это может привести к потере информации и сокращению ресурса микросхемы.

## 5.2.1.4 Повтор цикла чтения

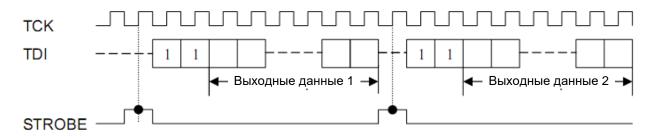

Временная диаграмма повтора цикла чтения приведена на рисунке 11.

Рисунок 11 – Повтор цикла чтения

Если предыдущим режимом был цикл чтения и текущий стартовый символ 11, происходит повтор цикла чтения. Данные по адресу, равному предыдущему адресу плюс единица, выводятся на выход TDI последовательно младшими разрядами вперед. После этого адрес автоматически инкрементируется и происходит ожидание следующего высокого уровня сигнала STROBE. Если следующий стартовый символ 11, происходит повтор чтения, а затем инкремент адреса и так далее. Разрядность данных соответствует разрядности данных предыдущего цикла чтения.

## 5.2.1.5 Повтор цикла записи

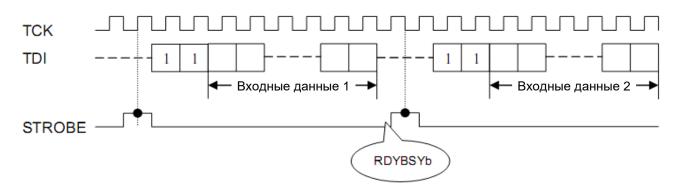

Временная диаграмма повтора цикла записи приведена на рисунке 12.

Рисунок 12 – Повтор цикла записи

Если предыдущим режимом работы был режим полного цикла и текущий стартовый символ 11, происходит повтор цикла записи данных, записываемых последовательно по линии TDI по адресу, равному предыдущему плюс единица. Затем происходит вывод состояния бита занятости RDYBSYb на выход TDI (аналогично режиму полного цикла). После окончания записи адрес автоматически инкрементируется и ожидается следующий высокий уровень сигнала STROBE. Если следующий стартовый символ 11, происходит повтор записи, а затем инкремент адреса и так далее. Разрядность данных соответствует разрядности данных предыдущего полного цикла.

## 5.3 Последовательный интерфейс SPI

Модуль памяти может управляться хост-контроллером, который выдает инструкции обычно в режиме мастер SPI. Мастер SPI соединяется с модулем памяти с помощью шины SPI, состоящей из четырех линий: nCE, SCK, SI, SO. Для выбора последовательного интерфейса в качестве основного используется линия SEL\_SPI (активный уровень — логическая «1»), при этом STROBE = 0. Значения сигналов для работы по последовательному интерфейсу SPI смотрите в таблице 3.

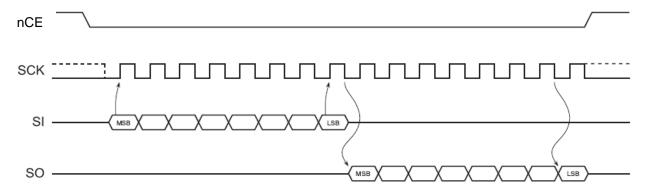

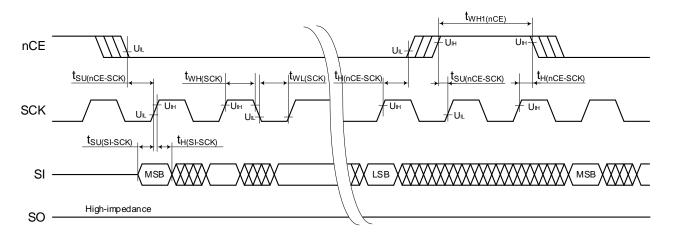

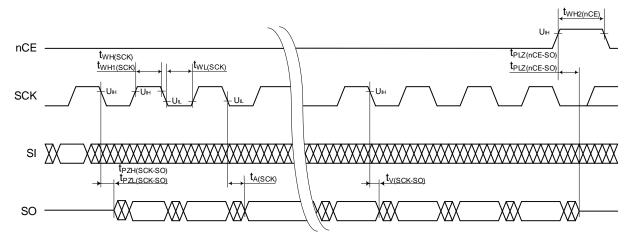

Протокол SPI имеет четыре режима работы (0, 1, 2 или 3), различие между которыми заключается в полярности и фазе сигнала SCK. Модуль памяти поддерживает два наиболее часто применяемых режима 0 и 3. Временная диаграмма режимов SPI 0 и 3 приведена на рисунке 13. Различие между ними заключается в неактивном состоянии линии SCK, когда мастер SPI в режиме отсутствия передачи данных. В обоих режимах данные всегда захватываются с шины по переднему фронту SCK и всегда выставляются на шину по заднему фронту SCK.

Рисунок 13 – Временная диаграмма режимов SPI 0 и 3

#### 5.3.1 Команды и адресация

Допустимые инструкции или операции всегда должны начинаться установкой в активное состояние линии nCE. После того как nCE установлен, хост-контроллер должен выставить на шину SPI достоверный 8-разрядный код операции. Затем, в зависимости от типа операции, выставляются адрес и (или) данные, тактируемые хост-контроллером. Все коды операций, адреса и данные передаются на шину старшими разрядами вперед (MSB). Операция заканчивается переводом линии nCE в неактивное состояние.

Коды операций, не поддерживаемые модулем памяти, игнорируются, и операция не стартует. Микросхема также игнорирует данные на входе SI до тех пор, пока не стартует следующая операция (пСЕ линия должна быть установлена в неактивное состояние, а затем переведена в активное состояние). Если линия пСЕ переводится в неактивное состояние, прежде чем закончится передача кода операции и адресной информации, операция не начнется и модуль памяти вернется в неактивное состояние для ожидания следующей операции.

Для передачи адреса, состоящего из адресных битов A20-A0, необходимо послать 3 байта информации по шине SPI. Адресные биты A23-A21, передаваемые по шине всегда игнорируются, так как максимально адресуемый диапазон адресов модуля памяти 000000h-1FFFFFh.

Перечень поддерживаемых команд приведен в таблице 9. Описание команд приведено в последующих разделах.

Таблица 9 – Перечень поддерживаемых команд

| Команда                         | Тип     | Volumentary   | Частота, | Байт   | Байт      | Байт   |

|---------------------------------|---------|---------------|----------|--------|-----------|--------|

| Команда                         | команды | Код команды   | МΓц      | адреса | фиктивных | данных |

| Read Array                      | R       | 03h 0000 0011 | до 15    | 3      | 0         | 1      |

|                                 |         | 0Bh 0000 1011 | до 30    | 3      | 1         | 1      |

| Sector Erase                    | W       | D8h 1101 1000 | до 50    | 3      | 0         | 0      |

| Chip Erase                      | W       | 60h 0110 0000 | до 50    | 0      | 0         | 0      |

| Byte Program                    | W       | 02h 0000 0010 | до 50    | 3      | 0         | 1      |

| Write Enable                    | W       | 06h 0000 0110 | до 50    | 0      | 0         | 0      |

| Write Disable                   | W       | 04h 0000 0100 | до 50    | 0      | 0         | 0      |

| Protect Sector                  | W       | 36h 0011 0110 | до 50    | 3      | 0         | 0      |

| Unprotect Sector                | W       | 39h 0011 1001 | до 50    | 3      | 0         | 0      |

| Read Sector Protection Register | R       | 3Ch 0011 1100 | до 30    | 3      | 0         | 1      |

| Read Status Register            | R       | 05h 0000 0101 | до 30    | 0      | 0         | 1      |

| Write Status Register           | W       | 01h 0000 0001 | до 50    | 0      | 0         | 1      |

| Reset                           | W       | F0h 1111 0000 | до 50    | 0      | 0         | 1      |

| Read ID устройства и            | R       | 9Fh 1001 1111 | до 30    | 0      | 0         | 2      |

| производителя                   |         |               |          |        |           |        |

$\Pi$  р и м е ч а н и е — Обозначения типа команд:

W – команда записи;

R – команда чтения

Если линия nCE установлена в неактивное состояние, и при этом не выполняется операция стирания или программирования, то микросхема переходит в режим хранения. В режиме хранения ток потребления значительно понижается.

Для входа в режим хранения на вывод nCE необходимо подать напряжение  $U_{CC}\pm0.3$  B, более ограниченный диапазон, чем  $U_{IH}$ . Если  $U_{IH}\leq U_{nCE}< U_{CC}$  - 0,3 B, то микросхема будет находиться в режиме хранения, однако ток потребления будет больше.

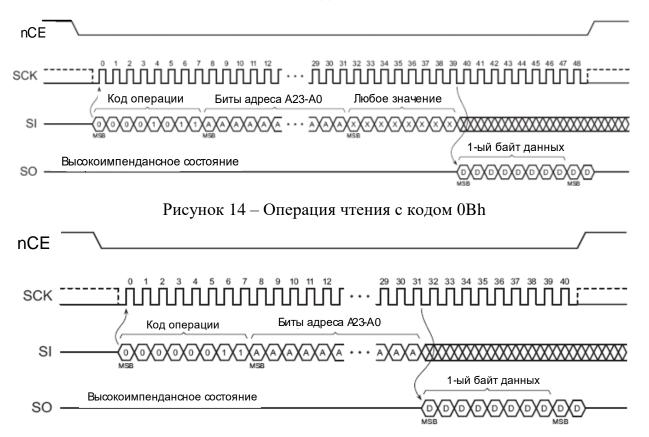

## 5.3.2 Операция чтения массива данных

Команда «Read Array» может применяться при чтении непрерывного потока данных из модуля памяти, обеспечивая тактирование на линии SCK, установив стартовый адрес один раз. Модуль памяти содержит внутренний счетчик адреса, который автоматически инкрементируется на каждом периоде тактовых импульсов. Два кода операции (0Bh и 03h) могут быть использованы для команды «Read Array». Применение каждого из кодов зависит от максимальной частоты тактовых сигналов, которая используется для чтения данных из микросхемы. Код операции 03h используется для наименьшей частоты до 15 МГц, код операции 0Bh используется для максимальной частоты до 30 МГц.

Для выполнения операции чтения линия nCE должна быть установлена в активное состояние и соответствующий код операции передан в микросхему. После передачи кода

операции должны быть переданы 3 байта адреса, определяющие стартовый адрес первого байта для чтения внутри массива данных. Следом за адресными байтами может передаваться фиктивный байт в зависимости от кода операции, используемой в команде «Read Array». Если используется код операции 0Bh, передается один фиктивный байт.

После передачи всей необходимой командной последовательности производится считывание данных на линии SO. Данные всегда выставляются старшими разрядами вперед (MSB). Если считан последний байт (адрес 1FFFFh) массива памяти, микросхема продолжает чтение с начала массива (адрес 000000h). Задержек при этом не происходит.

При установке линии nCE в неактивное состояние операция чтения прекращается, и линия SO переходит в высокоимпедансное состояние. Операция чтения может быть прервана в любой момент.

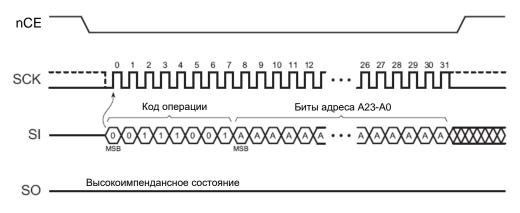

Временные диаграммы операций чтения с кодом 0Bh и кодом 03h приведены на рисунках 14, 15.

Не обязательно читать полный байт данных.

Рисунок 15 – Операция чтения с кодом 03h

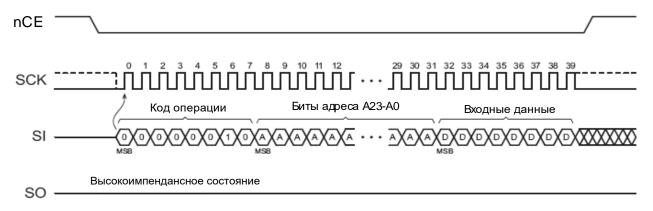

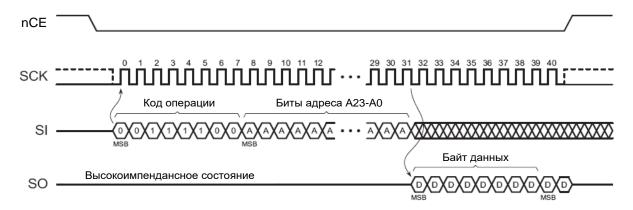

#### 5.3.3 Операция программирования байта

Команда «Byte Program» позволяет запрограммировать один байт данных в предварительно стертую ячейку модуля памяти. При стирании ячейки памяти все 8 бит устанавливаются в состояние логической «1» (значение FFh). Перед выполнением команды «Byte Program» необходимо выполнить команду «Write Enable», чтобы установить бит WEL регистра статуса в логическую «1».

Для выполнения команды «Byte Program» необходимо передать в модуль памяти код операции 02h, три адресных байта и байт данных для программирования. После перевода линии nCE в неактивное состояние микросхема начнет программирование байта

в ячейку памяти с адресом, переданным в команде «Вуte Program». Перевод линии пСЕ в неактивное состояние должен происходить на границе байта, т.е. кратно 8 бит, в противном случае модуль памяти прервет операцию, и данные не будут запрограммированы в ячейку памяти. Если адрес ячейки в пределах сектора, находящегося в защищенном состоянии, операция программирования байта не будет выполнена, модуль памяти вернется в неактивное состояние после перевода линии пСЕ в логическую «1». Значение бита WEL в регистре статуса будет сброшено в состояние логического «0», если операция программирования прервана неполным адресом или данными, или была попытка программирования в защищенный сектор.

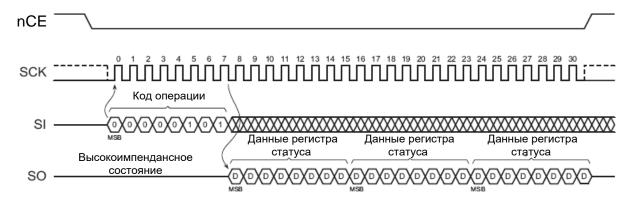

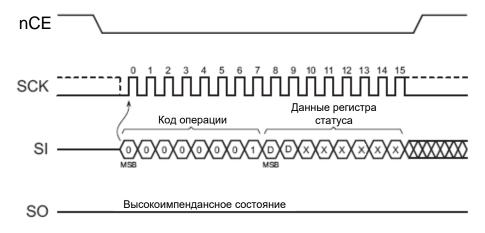

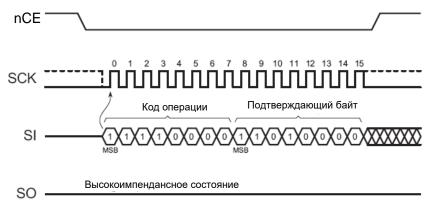

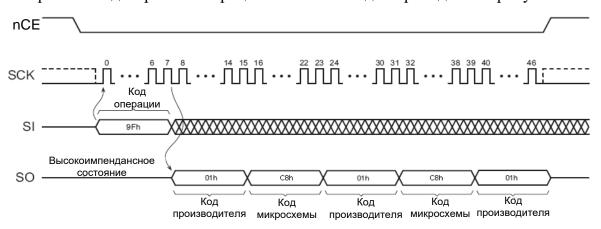

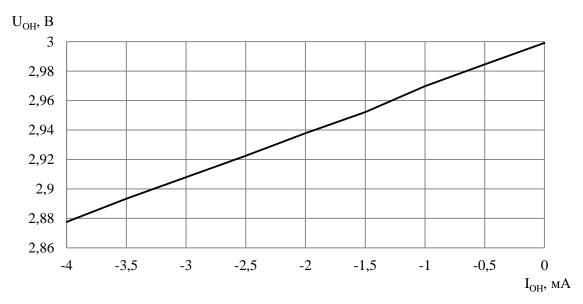

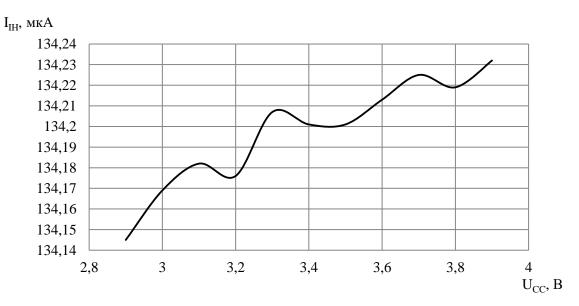

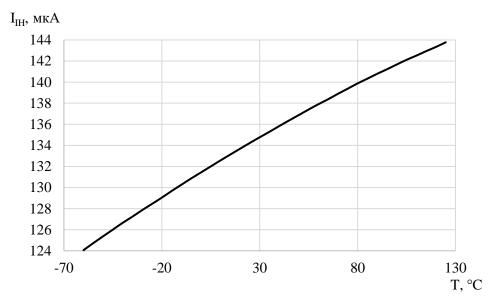

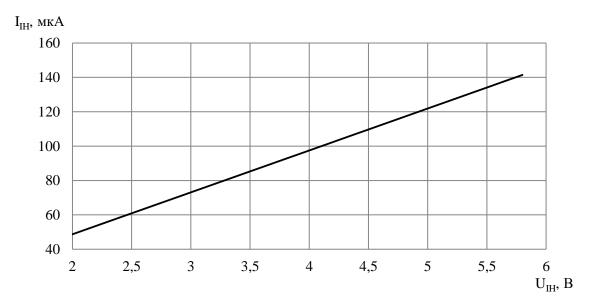

Максимальное время, необходимое для программирования байта, -  $t_{CYP\_BYT}$ . Это значение соответствует минимальному времени таймаута обращения к модулю памяти без отслеживания статуса выполнения операции. Во время операции программирования рекомендуется пользоваться операцией чтения регистра статуса, который показывает состояние занятости модуля памяти. Это позволит сократить время ожидания выполнения операции. Перед завершением операции программирования бит WEL регистра статуса сбросится в состояние логического «0».