[i] Режимы запуска МК К1986ВЕ1QI (К1986ВЕ1FI, К1986ВЕ1GI)

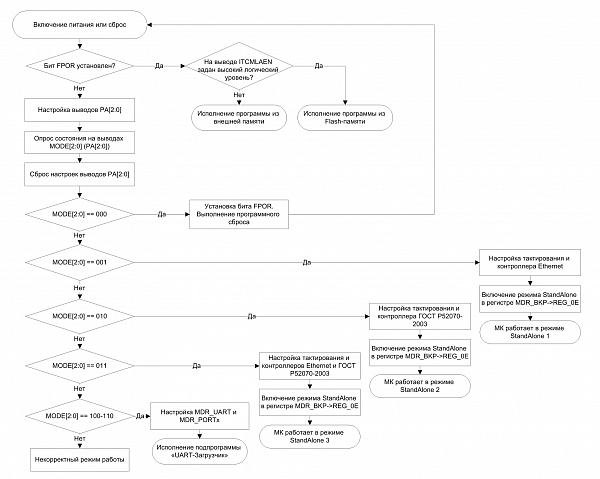

На рисунке 1 приведена диаграмма запуска МК К1986ВЕ1QI.

Рисунок 1 - Диаграмма запуска МК К1986ВЕ1QI

В МК К1986ВЕ1QI таблица векторов прерываний не может быть перенесена и всегда располагается с адреса 0x0000_0000. В связи с этим в МК с адреса 0x0000_0000 предусмотрен доступ к трём областям памяти, предназначенных для хранения программы. В ходе работы МК в адресное пространство, начиная с адреса 0x0000_0000, может отображаться одна из следующих областей памяти:

-

BOOT ROM (0x0000_0000 - 0x0000_07FF) – область памяти с загрузочной программой (масочное ПЗУ) объёмом 2 Кбайт;

-

EEPROM (0x0000_0000 - 0x0001_FFFF) – область Flash-памяти программ объёмом 128 Кбайт;

-

External code (0x0000_0000 - 0x000F_FFFF) – область доступа к внешней системной шине объёмом 1 Мбайт.

Область памяти, которая отображается с адреса 0х0000_0000, определяется значением бита FPOR регистра BKP_REG_0E и состоянием на выводе ITCMLAEN, таблица 1.

Таблица 1 – Отображение различных областей памяти в адресное пространство, начиная с адреса 0х0000_0000, в зависимости от FPOR и ITCMLAEN

|

Бит FPOR регистра BKP_REG_0E |

Логический уровень на выводе ITCMLAEN |

Область памяти, отображаемая с адреса 0x0000_0000 |

| 0 | X | BOOT ROM (0x0000_0000 - 0x0000_07FF) |

| 1 | 0 |

External code (0x0000_0000 - 0x000F_FFFF) |

| 1 | EEPROM (0x0000_0000 - 0x0001_FFFF) |

Включение питания

После включения питания бит FPOR сброшен, и МК начинает выполнять загрузочную программу из области памяти BOOT ROM. По состоянию выводов MODE[2:0] (PA[2:0]) загрузочная программа определяет, в каком из режимов будет функционировать МК. Перед опросом состояния этих выводов, для них включается внутренняя подтяжка к шине «Общий» (встроенные резисторы подтяжки к шине «Общий» имеют сопротивление ~50 кОм). Считывание состояния выводов MODE[2:0] выполняется не сразу после запуска загрузочной программы, подробнее описано ниже в пункте «Время запуска МК до опроса выводов MODE[2:0]». В дальнейшем выводы MODE[2:0] (PA[2:0]) могут использоваться в пользовательской программе.

Сброс МК

После программного сброса (регистр SCB->AIRCR), аппаратного сброса (вывод nRESET) или сброса от сторожевого таймера МК начинает выполнение из области памяти, определяемой значениями FPOR и ITCMLAEN.

Значение бита FPOR определяется выбранным режимом работы после включения питания. Если перед сбросом МК работал в режиме MODE[2:0] = 000, «Микроконтроллер с режимом отладки», то бит FPOR был установлен загрузочной программой, поэтому после сброса будет выполнен запуск из области памяти, определяемой состоянием на выводе ITCMLAEN – EEPROM или External code. Бит FPOR сбрасывается только по сбросу при включении основного и батарейного питания, поэтому область памяти BOOT ROM в данном случае становится не доступна до повторного включения питания.

Если перед сбросом МК работал в режиме «StandAlone1-3», MODE[2:0] = 001-011, или в режиме «UART загрузчик», MODE[2:0] = 100-110, то бит FPOR не был установлен загрузочной программой, поэтому после сброса будет выполнен запуск загрузочной программы из области BOOT ROM.

Режимы работы

Таблица 2 – Режимы первоначального запуска МК|

MODE[2:0] |

Режим |

Стартовый адрес/ таблица векторов прерываний |

Описание |

|

000 |

Микроконтроллер с режимом отладки |

0х0000_0000 |

Процессор начинает выполнять программу из внутренней FLASH памяти программ. При этом разрешается работа отладочного интерфейса JTAG Сигнал выбора памяти программ: ITCMLAEN=1 - внутренняя память. ITCMLAEN=0 - внешняя память |

|

001 |

Режим Stand alone1 |

0х0000_0000 |

Процессор конфигурирует прямой доступ к контроллеру Ethernet с помощью внешней системной шины и переходит в режим сброса. Частота задаётся внешним генератором HSE/2, умноженная на 4 с помощью PLL. Адрес – {PC[3],PB[11:0]} Данные – PA[15:0] Byte enable – PB[13:12] Chip enable – PB[15:14] Write enable – PC[0] Output enable – PC[1] Вход ITCMLAEN=1 |

|

010 |

Режим Stand alone2 |

0х0000_0000 |

Процессор конфигурирует прямой доступ к контроллеру интерфейса ГОСТ Р52070-2003 с помощью внешней системной шины и переходит в режим сброса. Частота задаётся внешним осциллятором HSE, умноженная на 10 с помощью PLL. Адрес – {PC[3],PB[11:0]} Данные – {PC[6:4],PA[15:0]} Chip enable – PB[15:14] Write enable – PC[0] Output enable – PC[1] Вход ITCMLAEN=0 |

|

011 |

Режим Stand alone3 |

0х0000_0000 |

Процессор конфигурирует прямой доступ к контроллерам Ethernet и интерфейса ГОСТ Р52070-2003 с помощью внешней системной шины и переходит в режим сброса. Частота задаётся внешним генератором HSE/2, умноженная на 4 с помощью PLL. Вход ITCMLAEN=1 – доступ к контроллеру Ethernet. Вход ITCMLAEN=0 – доступ к контроллеру интерфейса ГОСТ Р 52070-2003 |

|

100-110 |

UART загрузчик |

Определяется пользователем / 0х0000_0000 |

Микроконтроллер через интерфейс UART1 на выводах PC[4:3] получает код программы в ОЗУ для исполнения |

|

111 |

Зарезервировано |

- |

- |

Режим «Микроконтроллер с режимом отладки», MODE[2:0] = 000

После определения данного режима работы загрузочная программа выполняет следующие действия:

- устанавливает бит FPOR регистра BKP_REG_0E, после чего происходит сброс МК;

- если ITCMLAEN = 1, то начинается выполнение программы из Flash-памяти МК;

- если ITCMLAEN = 0:

-- в контроллере внешней системной шины настраивается режим работы с памятью ROM, устанавливается WAIT_STATE[3:0] = 0xF и положительная полярность сигнала CLOCK. Параметры контроллера внешней шины могут быть изменены программно;-- аппаратно настраиваются выводы для работы с внешней памятью:

- шина данных D[31:0] ( {PB[15:0], PA[15:0]} );

- шина адреса A[16:0] ( {PE[2:0], PD[15], PF[15:3]} );

- сигнал записи данных nWR ( PC[0] );

- сигнал чтения данных nRD ( PC[1] );

- сигнал синхронизации CLKO ( PC[3] );

Для доступа к Flash-памяти при ITCMLAEN = 0 (внешняя память) в МК предусмотрен бит ITCMUAEN регистра ACTLR:

- при ITCMUAEN = 0 в адресное пространство 0x10000000-0x1FFFFFFF отображается область памяти External code;

- при ITCMUAEN = 1 в адресное пространство 0x10000000-0x1000FFFF отображается область памяти EEPROM.

Режим «StandAlone1», MODE[2:0] = 001 (доступ к Ethernet)

Для работы в данном режиме на вход HSE, вывод OSC_IN, должен быть подключён внешний генератор 25 МГц, на выводе ITCMLAEN должен быть установлен уровень логической единицы.

После определения данного режима работы загрузочная программа выполняет следующие действия:

- настраивает тактирование МК: частота задаётся внешним генератором HSE/2, умноженная на 4 с помощью PLL, итоговая частота составляет 50 МГц;

- включает тактирование контроллера Ethernet и блока PHY в регистре ETH_CLOCK;

- включает режим StandAlone в регистре BKP_REG_0E.

После включения режима StandAlone аппаратно настраиваются выводы внешней шины и контроллера Ethernet, приведённые в спецификации, пункт «Описание выводов», таблица – «Описание выводов микроконтроллера в режиме Stand Alone».

Режим «StandAlone2», MODE[2:0] = 010 (доступ к контроллеру ГОСТ Р52070-2003)

Для работы в данном режиме к HSE, выводы OSC_IN и OSC_OUT, должен быть подключён внешний кварцевый резонатор 8 МГц, на выводе ITCMLAEN должен быть установлен уровень логического нуля.

После определения данного режима работы загрузочная программа выполняет следующие действия:

- настраивает тактирование МК: частота задаётся внешним HSE, умноженная на 10 с помощью PLL, итоговая частота составляет 80 МГц;

- включает тактирование контроллера ГОСТ Р52070-2003;

- включает режим StandAlone в регистре BKP_REG_0E.

После включения режима StandAlone аппаратно настраиваются выводы внешней шины и контроллера ГОСТ Р52070-2003, приведённые в спецификации, пункт «Описание выводов», таблица – «Описание выводов микроконтроллера в режиме Stand Alone».

Режим «StandAlone3», MODE[2:0] = 011 (доступ к контроллерам ГОСТ Р52070-2003 и Ethernet)

Для работы в данном режиме на вход HSE, вывод OSC_IN, должен быть подключён внешний генератор 25 МГц, логический уровень на выводе ITCMLAEN устанавливает активный контроллер: ГОСТ Р52070-2003 при ITCMLAEN = 0, Ethernet при ITCMLAEN = 1.

После определения данного режима работы загрузочная программа выполняет следующие действия:

- настраивает тактирование МК: частота задаётся внешним генератором HSE/2, умноженная на 4 с помощью PLL, итоговая частота составляет 50 МГц;

- включает тактирование контроллера Ethernet и блока PHY в регистре ETH_CLOCK;

- включает тактирование контроллера по ГОСТ Р52070-2003;

- включает режим StandAlone в регистре BKP_REG_0E.

После включения режима StandAlone аппаратно настраиваются выводы внешней шины и контроллеров Ethernet и ГОСТ Р52070-2003, приведённые в спецификации, пункт «Описание выводов», таблица – «Описание выводов микроконтроллера в режиме Stand Alone».

Режим «UART загрузчик», MODE[2:0] = 100-110

После определения данного режима работы загрузочная программа выполняет следующие действия:

- в контроллере портов ввода-вывода настраивает выводы для работы UART1: TX – PC[3] и RX – PC[4];

- настраивает контроллер UART1 со следующими параметрами:

- начальная скорость – 9600 Бод;

- количество бит данных – 8;

- четность – нет;

- количество Stop-бит – 1;

- загрузчик не использует FIFO UART1;

- загрузчик всегда выступает в качестве Slave, а внешнее устройство, подающее команды, – в качестве Master;

- данные передаются младшим битом вперед;

- ожидает принятия по интерфейсу UART команды.

Время запуска МК до опроса выводов MODE[2:0]

В зависимости от события запуска: включение питания либо снятие активного уровня с вывода nRESET, удержание МК в состоянии сброса выполняется различное время (спецификации, раздел "8 Схема сброса при включении и выключении основного питания"):

- при включении питания после превышения Ucc = 2,0 В МК удерживается в сбросе ~4 мс;

- после снятия активного уровня с вывода nRESET МК удерживается в сбросе ~20 мкс.

После выхода из состояния сброса начинает выполняться загрузочная программа. При частоте внутреннего генератора HSI = 6,72 МГц для МК К1986ВЕ1QI были получены следующие времена работы загрузочной программы:

- до перехода в main() выполняется инициализация окружения Си (инициализация стека, кучи, глобальных переменных и т.д.), это время составляет порядка 250 мкс;

- после входа в main() выполняется инициализация выводов MODE[2:0], задержка, а затем считывание значений MODE[2:0], это время составляет порядка 100 мкс.

При других значениях частоты генератора HSI (от 6 до 10 МГц) время выполнения загрузочной программы будет пропорционально изменяться.

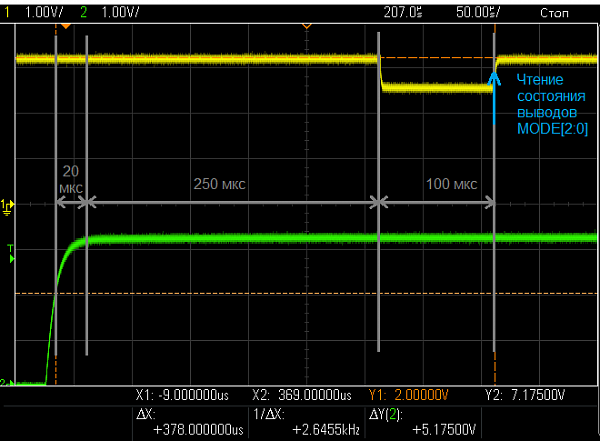

Осциллограмма запуска МК К1986ВЕ1QI после снятия активного уровня с вывода nRESET приведена на рисунке 2, при этом установлен режим MODE[2:0] = 100 – «UART загрузчик», HSI = 6,72 МГц, жёлтый луч - вывод MODE[2] (PA2), зелёный луч - вывод nRESET, время после деактивации nRESET и до момента считывания выводов MODE[2:0] составляет порядка 370-380 мкс. Уменьшение уровня напряжения на выводе MODE[2] (PA2) обусловлено образовавшимся делителем напряжения после включения внутренних резисторов подтяжки к земле. Считывание значений с выводов MODE[2:0] происходит перед отключением внутренних резисторов подтяжки к земле.

Рисунок 2 – Осциллограмма запуска МК К1986ВЕ1QI после снятия активного уровня с nRESET, жёлтый луч - вывод MODE[2] (PA2), зелёный луч - вывод nRESET

Сохранить статью в PDF