[i] Временные характеристики выходных данных порта связи

Для микросхем К1967ВН044 (К1967ВН04BG) в спецификации приводится информация о временных характеристиках выходных данных порта связи. Рассмотрим логику процесса более подробно.

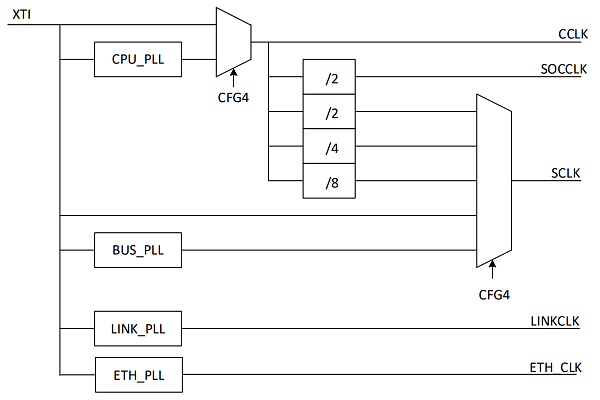

Внутренняя логика передатчика LINK-порта работает на частоте LINKCLK, которая формируется из LINK_PLL (рисунок 1).

Рисунок 1 - Источники тактовой частоты

При этом выходная частота LINK-порта на LxCLKO равна половине частоты LINKCLK, а частота изменения данных равна частоте LINKCLK (поскольку данные изменяются дважды за период частоты на LxCLKO).

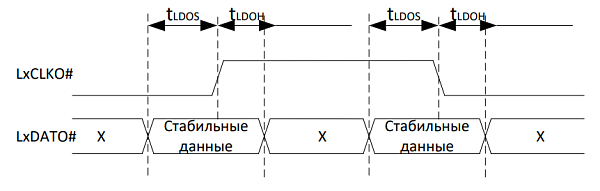

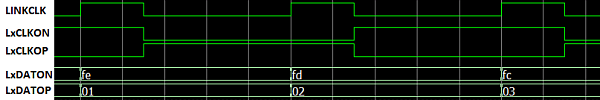

На рисунке 2 приведена временная диаграмма выходных данных порта связи и выхода синхронизации LxCLKO, на рисунке 3 - временная диаграмма сигналов при работе передатчика.

Рисунок 2 - Временная диаграмма выходных данных LINK-порта

Рисунок 3 - Временная диаграмма сигналов передатчика LINK-порта

Как можно видеть из рисунка 3, данные переключаются по фронту внутренней частоты LINKCLK, а выходной синхросигнал - по срезу. При этом важно отметить, что на рисунке 3 коэффициент заполнения внутренней частоты LINKCLK составляет не 50%, что может быть в частном случае (о чем будет указано ниже). В общем случае коэффициент заполнения будет 50% и времена предустановки и удержания данных будут примерно равны, данные переключаются посередине удержания уровня на LxCLKO. Для обеспечения наилучших временных характеристик для выходных данных (как в таблице в спецификации) частота должна иметь коэффициент заполнения 50% (или максимально близко к нему). В таблице в спецификации времена сняты при внутренней частоте LINKCLK 100 МГц с коэффициентом заполнения 50%.

Вне зависимости от коэффициента заполнения частоты LINKCLK частота синхросигнала LxCLKO на выводе всегда будет иметь коэффициент заполнения 50%.

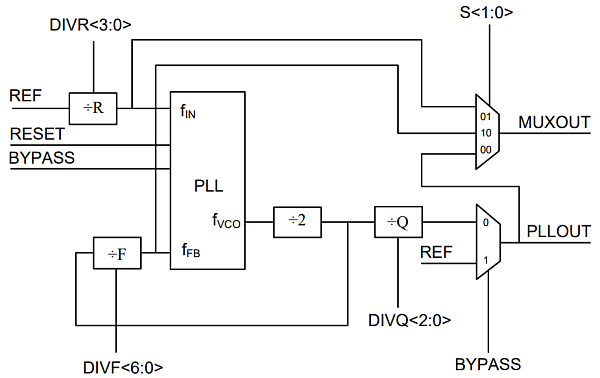

Как было указано ранее, в общем случае коэффициент заполнения внутренней частоты LINKCLK, от которой зависят времена предустановки и удержания выходных данных LxDATO, составляет 50 %. На практике коэффициент заполнения зависит от настроек LINK_PLL - как приведено на рисунке 1, частота LINKCLK формируется из LINK_PLL. Структура блока LINK_PLL приведена на рисунке 4.

Рисунок 4 - Структура PLL

Частота на выходе блока PLL (PLLOUT) может формироваться:

-

При BYPASS = 0: c выхода аналогового блока PLL (fVCO). При этом эта частота всегда делится на 2, и опционально на доп. делитель по степеням 2 , что совокупно всегда обеспечивает коэффициент заполнения 50%.

-

При BYPASS =1: со входа REF (он же XTI/OSCI), в таком случае коэффициент заполнения будет зависеть напрямую от OSCI.

Здесь нужно отметить, что по сбросу BYPASS = 0, однако устанавливается в 1 в загрузочной программе при загрузке в режиме "Загрузка через LINK-порты (любой) в однобитовом режиме".

Частота XTI/OSCI формируется, в зависимости от состояния вывода PC[30] во время сброса, используя внешних кварцевый резонатор на выводах OSCI/OSCO (при PC30 = 0) или внешний генератор на OSCI (при PC30 = 1 или в неподключенном состоянии). Выходная скважность при этом не контролируется.

Таким образом, при работе передатчика LINK-порта для обеспечения наилучших времен предустановки и удержания LxDATO необходимо всегда использовать аналоговый блок PLL (BYPASS = 0), что обеспечит переключение данных в середине удержания уровня синхросигнала LxCLKO.Сохранить статью в PDF