62901

[i] Пример работы с АЦП К5101НВ015 на отладочной плате К1967ВН044

Дата последнего изменения: 20.01.2026 16:52:57

В данной статье рассмотрен пример работы с АЦП К5101НВ015 на отладочной плате для процессора К1967ВН044. Проект для среды CM-LYNX приложен в конце статьи - "Файлы для скачивания".

В процессорах К1967ВН044, К1967ВН04BG реализовано два LINK-порта связи, работающих по стандарту LVDS. LINK-порты связи позволяют обеспечить взаимодействие с различными внешними устройствами, например, АЦП, ЦАП, процессоры К1967ВН02BG и К1967ВН044 (и К1967ВН04BG). Для работы с микросхемами АЦП и ЦАП в контроллер портов связи процессора К1967ВН044 (и К1967ВН04BG) были добавлены специальные функции, позволяющие выполнять гибкую настройку приёмника и передатчика. Так, например, при приёме данных от АЦП есть возможность выбрать разрядность данных (10, 12, 14 или 16 бит), порядок приёма данных (четные биты передаются по фронту, нечетные по срезу), а также установить аппаратное преобразование из смещённого в дополнительный код (спецификация, таблица 127 – «Регистр LRCTL»).

Для демонстрации возможностей процессора К1967ВН044 по работе с внешним АЦП на отладочных платах установлена микросхема К5101НВ015.

Инициализация АЦП выполняется по интерфейсу SPI. Так как подключение SPI сигналов от АЦП выполнено к выводам процессора, не имеющих функции для работы с контроллером SPI, то для взаимодействия с АЦП используется программная реализация SPI-интерфейса. В процессе инициализации АЦП также выполняется процедура калибровки.

После настройки процессора и АЦП осуществляется следующий алгоритм работы:

Параметры, используемые при анализе полученных данных, приведены в файле "analyze_adc_data.h":

SAMPLE_RATE_CLK = 20 МГц – тактовая частота АЦП;

INPUT_FREQ_1- INPUT_FREQ_3 = {2, 4, 8 МГц} – искомые частоты основных гармоник.

В качестве тактовой частоты АЦП используется сигнал, поданный на разъём X1. Входной сигнал для преобразования подаётся на разъём X17. Опорное напряжение АЦП задаётся внутренним источником UREFI = 1 В.

Вход АЦП OEN (разрешение выходов Q[13:0], CLKO, nCLKO) подтянут на плате с помощью резистора к шине общий, поэтому пока процессор не подаст на OEN напряжение высокого логического уровня, АЦП не будет выдавать данные.

Подключение шины данных АЦП К5101НВ015 к процессору К1967ВН044 выполнено по интерфейсу LVDS к LINK-порту 0, поэтому режим LVDS выбран по умолчанию (LVDSEN = 1). При передаче данных от АЦП к процессору есть особенность: АЦП передаёт чётные биты по срезу CLKO, а нечётные по фронту CLKO, при этом процессор ожидает получить данные наоборот - четные биты по фронту, а нечетные по срезу. На плате для обеспечения аппаратной совместимости тактовый сигнал CLKO от АЦП инвертирован (CLKO подключен к L0CLKIN, а nCLKO подключен к L0CLKIP).

Вывод Q12SEL подтянут на плате с помощью резистора R116 к питанию 1,8 В, поэтому АЦП работает в 12-разрядном режиме выходов (Q0 и Q1 находятся в высокоимпедансном состоянии). Необходимо отметить, что к процессору К1967ВН044 подключены все выходные линии Q0-Q13, а вывод Q12SEL имеет внутреннюю подтяжку к шине общий. Таким образом можно выбрать 14-разрядный режим работы выходов АЦП, убрав резистор R116.

Сохранить статью в PDF

В процессорах К1967ВН044, К1967ВН04BG реализовано два LINK-порта связи, работающих по стандарту LVDS. LINK-порты связи позволяют обеспечить взаимодействие с различными внешними устройствами, например, АЦП, ЦАП, процессоры К1967ВН02BG и К1967ВН044 (и К1967ВН04BG). Для работы с микросхемами АЦП и ЦАП в контроллер портов связи процессора К1967ВН044 (и К1967ВН04BG) были добавлены специальные функции, позволяющие выполнять гибкую настройку приёмника и передатчика. Так, например, при приёме данных от АЦП есть возможность выбрать разрядность данных (10, 12, 14 или 16 бит), порядок приёма данных (четные биты передаются по фронту, нечетные по срезу), а также установить аппаратное преобразование из смещённого в дополнительный код (спецификация, таблица 127 – «Регистр LRCTL»).

Для демонстрации возможностей процессора К1967ВН044 по работе с внешним АЦП на отладочных платах установлена микросхема К5101НВ015.

1. Описание примера работы с АЦП К5101НВ015

В примере показана процедура настройки процессора К1967ВН044 (К1967ВН04BG) и АЦП К5101НВ015. Для приёма данных от АЦП настраивается LINK-порт связи 0, для копирования полученных отсчётов из буфера порта связи в внутреннюю ОЗУ настраивается 8 канал DMA.Инициализация АЦП выполняется по интерфейсу SPI. Так как подключение SPI сигналов от АЦП выполнено к выводам процессора, не имеющих функции для работы с контроллером SPI, то для взаимодействия с АЦП используется программная реализация SPI-интерфейса. В процессе инициализации АЦП также выполняется процедура калибровки.

После настройки процессора и АЦП осуществляется следующий алгоритм работы:

- Ожидается завершение работы DMA (флаг adc_dma_done).

- DMA копирует принятые данные из буфера порта связи в ОЗУ. По окончании передачи заданного количества данных (ADC_DMA_BUF_SIZE) DMA останавливается и возникает прерывание.

- В обработчике прерывания от DMA устанавливается флаг adc_dma_done, а также переключается состояние на выводе FLAG0. Переключение светодиода FLAG0 позволяет определить время выполнения одного цикла.

- В основном цикле вызывается функция для анализа полученных данных.

- В качестве анализа выполняется вычисление частотного спектра с помощью алгоритма БПФ, после чего определяется частота основной гармоники. Если частота основной гармоники совпадает с одной из указанных в примере (это 2 МГц, 4 МГц, 8 МГц), то загорается один из светодиодов FLAG1-FLAG3.

- После анализа запускается DMA для приёма данных и цикл повторяется.

Параметры, используемые при анализе полученных данных, приведены в файле "analyze_adc_data.h":

SAMPLE_RATE_CLK = 20 МГц – тактовая частота АЦП;

INPUT_FREQ_1- INPUT_FREQ_3 = {2, 4, 8 МГц} – искомые частоты основных гармоник.

2. Особенности работы с АЦП К5101НВ015 на отладочной плате

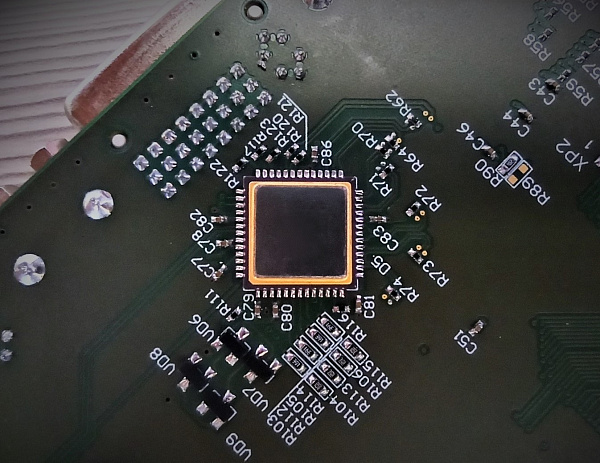

Рисунок 1 - Микросхема АЦП К5101НВ015 на модуле процессорномВ качестве тактовой частоты АЦП используется сигнал, поданный на разъём X1. Входной сигнал для преобразования подаётся на разъём X17. Опорное напряжение АЦП задаётся внутренним источником UREFI = 1 В.

Вход АЦП OEN (разрешение выходов Q[13:0], CLKO, nCLKO) подтянут на плате с помощью резистора к шине общий, поэтому пока процессор не подаст на OEN напряжение высокого логического уровня, АЦП не будет выдавать данные.

Подключение шины данных АЦП К5101НВ015 к процессору К1967ВН044 выполнено по интерфейсу LVDS к LINK-порту 0, поэтому режим LVDS выбран по умолчанию (LVDSEN = 1). При передаче данных от АЦП к процессору есть особенность: АЦП передаёт чётные биты по срезу CLKO, а нечётные по фронту CLKO, при этом процессор ожидает получить данные наоборот - четные биты по фронту, а нечетные по срезу. На плате для обеспечения аппаратной совместимости тактовый сигнал CLKO от АЦП инвертирован (CLKO подключен к L0CLKIN, а nCLKO подключен к L0CLKIP).

Вывод Q12SEL подтянут на плате с помощью резистора R116 к питанию 1,8 В, поэтому АЦП работает в 12-разрядном режиме выходов (Q0 и Q1 находятся в высокоимпедансном состоянии). Необходимо отметить, что к процессору К1967ВН044 подключены все выходные линии Q0-Q13, а вывод Q12SEL имеет внутреннюю подтяжку к шине общий. Таким образом можно выбрать 14-разрядный режим работы выходов АЦП, убрав резистор R116.

Сохранить статью в PDF

Файлы для скачивания

Документация

1.0.1 от 10.03.2026

2.6.3 от 07.11.2025

2.3.2 от 07.11.2025

Теги

Особенности применения "Know-How"