[i] Подключение выводов JTAG в микроконтроллерах

В спецификации на микроконтроллеры серии К1986ВЕ9х указано, что «при работе в режиме отладки разрешается работа отладочного интерфейса JTAG/SWD. При этом к микроконтроллеру может быть подключен JTAG/SWD адаптер, с помощью которого программные средства разработки позволяют работать с микроконтроллером в отладочном режиме. Линии JTAG должны быть подтянуты к питанию сопротивлениями не менее 10кОм с учетом того, чтобы эти подтяжки не влияли на работу системы».

Если в радиоэлектронном изделии для программирования микроконтроллера или отладки программы планируется использовать двухпроводной отладочный интерфейс SWD,

Все выводы JTAG-интерфейса микроконтроллера (nTRST, TCK, TMS, TDI, TDO) должны быть подключены, даже если в радиоэлектронном изделии для программирования микроконтроллера или отладки программы планируется использовать двухпроводной отладочный интерфейс SWD. После включения питания переход в режим SWD осуществляется из режима JTAG, поэтому все вывода интерфейса JTAG при старте микроконтроллера должны быть в определенном состоянии. После того, как микроконтроллер перешел в режим SWD, выводы JTAG можно не использовать до следующего сброса.

Выводы JTAG:

| Вывод JTAG | ULINK | ULINK2 | J-LINK Segger |

|---|---|---|---|

| nTRST | 100кОм pull-up к Vcc | 100кОм pull-up к Vcc | Двунаправленный вывод. Необходимо доопределение до Ucc. Номинал резисторов подтяжки, рекомендованный Segger, до 100кОм |

| TCK | 100кОм pull-up к Vcc | 100кОм pull-down к GND | Рекомендуется, чтобы было определённое состояние, но без уточнения, какое именно |

| TMS | 100кОм pull-up к Vcc | 100кОм pull-up к Vcc | Двунаправленный вывод. Необходимо доопределение до Ucc |

| TDI | 100кОм pull-up к Vcc | 100кОм pull-up к Vcc | Рекомендуется, чтобы было определённое состояние, но без уточнения, какое именно |

| TDO | Нет требований | Нет требований | Нет требований |

Выводы отладочного интерфейса SWD: SWD может применяться вместо JTAG. Используется двунаправленный вывод TMS (SWDIO), который обеспечивает JTAG-отладку и возможность работать в тестовом режиме, и TCK(SWDCLK). Во время взаимодействия с устройством, программатор обменивается данными по SWDIO(TMS) синхронно SWCLK. (для Segger J-Link бит данных передается или принимается по каждому фронту сигнала TCK)

| Вывод JTAG | ULINK | ULINK2 | J-LINK Segger |

|---|---|---|---|

| TCK | 100кОм pull-up к Vcc | 100кОм pull-down к GND | Рекомендуется, чтобы было определённое состояние, но без уточнения, какое именно |

| TMS | 100кОм pull-up к Vcc | 100кОм pull-up к Vcc | Двунаправленный вывод. Необходимо доопределение до Ucc |

| TDO | Нет требований(опциональный) | Нет требований(опциональный) | Нет требований (опциональный) |

Выбор номинала резистора для ULINK и ULINK2: http://www.keil.com/support/docs/3346.htm Можно использовать резисторы номиналом 10кОм или 100кОм (или любое другое значение из этого интервала). Важно, чтобы они использовались, тем самым защищая сигналы JTAG от неопределенного/произвольного состояния, когда выводы ни к чему не подсоединены.

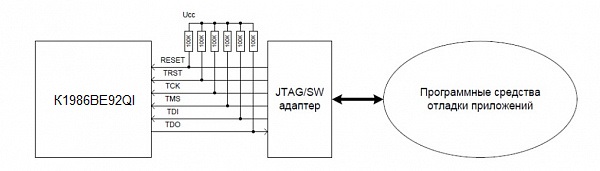

Рисунок 1 - Подключение выводов JTAG на примере микроконтроллера К1986ВЕ92QI

Подключение выводов JTAG для ULINK: https://developer.arm.com/documentation/ka003179/latest

Подключение выводов JTAG для ULINK2: https://developer.arm.com/documentation/101455/0100/Hardware-Description/Target-Connectors

Подключение выводов JTAG для SEGGER JLINK: https://wiki.segger.com/UM08001_J-Link_/_J-Trace_User_Guide

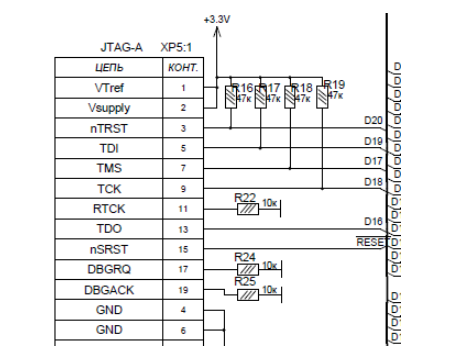

В отладочных платах вывод TDO подключен напрямую, без подтяжки к Ucc (рисунок 2):

Рисунок 2 - Реализация подключения выводов JTAG на отладочной плате

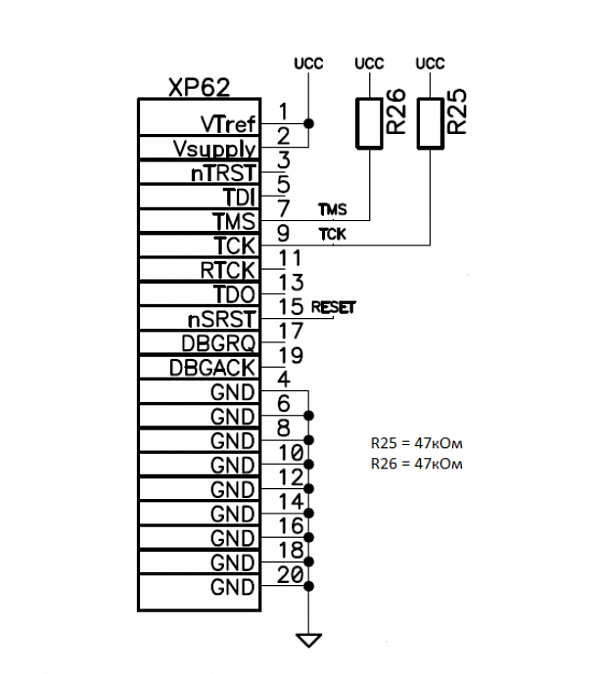

Если в микроконтроллере реализован только интерфейс SWD, то подключение выводов TMS и TCK - согласно рисунку 3 (в таком случае остальные выводы JTAG-интерфейса не используются или их нет в корпусе):

Рисунок 3 - Подключение выводов SWD на отладочной плате для микроконтроллера, в котором реализован только последовательный отладочный интерфейс SWD

Сохранить статью в PDF