[i] Микроконтроллер К1986ВЕ92У для конфигурирования ПЛИС серий 5576, 5578

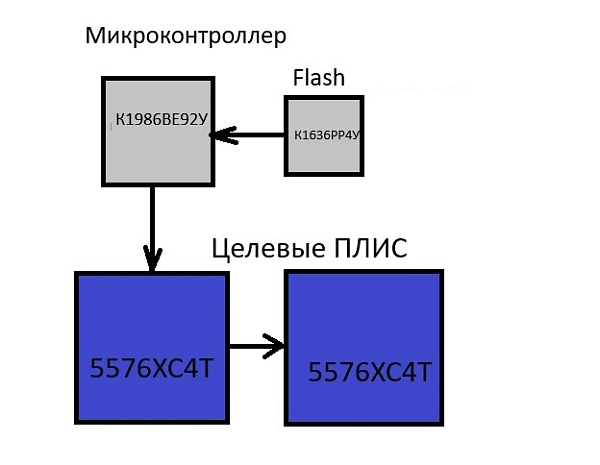

Рисунок 1 - Проектируемая схема

Для микроконтроллера К1986ВЕ92У разработан программный модуль конфигуратора ПЛИС в рамках макета, представленного на рисунке 2. Макет состоит из одной платы с микросхемой flash-памяти К1636РР4У и отладочного комплекта для микроконтроллера К1986ВЕ92У. Режим чтения flash-памяти - последовательный, режим конфигурирования ПЛИС - PS (пассивный последовательный). Третья плата, используемая в макете, - отладочная 5576ХС4Т.01. Она является целевой для конфигурирования ПЛИС 5576ХС4Т.

Архив проекта модуля можно скачать в конце статьи.

Рисунок 2 - Макет на базе микроконтроллера К1986ВЕ92У

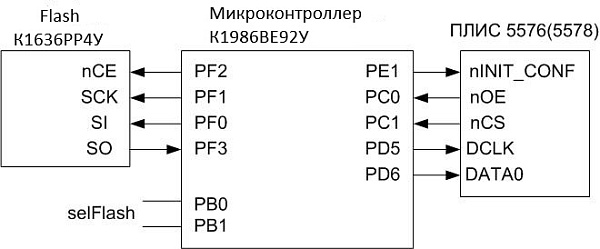

Общая схема подключения микроконтроллера К1986ВЕ92У, flash-памяти К1636РР4У и ПЛИС для режима PS представлена на рисунке 3. Выводы микроконтроллера К1986ВЕ92У, обозначенные на структурной схеме (рисунок 3) как selFlash, необходимы для выбора объёма подключаемой flash: 00 – 4Мбит, 01 – 16Мбит (например, К1636РР4У), 10 – 64Мбит, 11 – 256Mбит.

Рисунок 3 - Структурная схема соединения в режиме PS-конфигурирования ПЛИС

Время конфигурирования ПЛИС 5576ХС4 составляет 0,6 секунд при условии тактовой частоты ядра микроконтроллера К1986ВЕ92У 80МГц. Затраты по времени на конфигурирование при использовании загрузочного ППЗУ К5576РС1У этой же ПЛИС такие же.

Устройство программного модуля конфигуратора ПЛИС состоит из основных двух библиотечных файлов: FPGA_1986VE92.h, FPGA_1986VE92.c. В первом файле определены имена директив входов и выходов, объявлены переменные и функции. Во втором – описание функций.

В главном файле «main.с» программы имеется код, в котором инициализируется режим работы микроконтроллера, выполняется сброс ПЛИС перед конфигурированием, подготовка внешней flash для её работы. В главном цикле «while(1)» программы размещена основная функция для конфигурирования ПЛИС, чтение конфигурационных данных из flash и передачи их в ПЛИС. Осуществляется контроль состояния ПЛИС во время конфигурирования и после, а также сброс.

Пользовательский код может быть размещён после оператора множественного выбора «switch».

В проекте имеется всего одна глобальная переменная «done», которая выступает в качестве индикатора состояния ПЛИС: если «done=1» тогда ПЛИС сконфигурирована, если «done=0» - ПЛИС не сконфигурирована. Переменная объявлена в файле FPGA_1986VE92.h.

В файле FPGA_1986VE92.c размещены следующие функции:

- «void sendComFlash(void)» служит для формирования командной последовательности из 5 байт «0B 00 00 00 00» для инициализации режима чтения данных с автоинкрементом адреса flash типа К1636РР4У.

- «uint8_t resetFPGA(void)» необходима для сброса ПЛИС и вызова функции «void sendComFlash(void)». Алгоритм действий следующий, подаётся инверсный сигнал сброса ПЛИС на линию «nINIT_CONF» длительностью не менее 200 нс, одновременно вызывается функция «void sendComFlash(void)».

- «uint8_t modeFPGA(uint8_t)» выполняет основную роль для конфигурирования ПЛИС. Читает конфигурационные данные из flash и передаёт их в ПЛИС. Контролирует состояние ПЛИС во время конфигурирования и после, мониторингом линий nOE и nCS. а также имеется контроль ошибки CONF_DONE в случае не выхода ПЛИС на рабочий режим по переполнению «ind_byte» счётчика байт.

- «void delayFPGA(int)» является функцией программной задержки для формирования необходимых задержек сигнала сброса «nINIT_CONF» ПЛИС.

- «uint8_t reverseBits(uint8_t)» служит для реверса бит в конфигурационных байтах данных ПЛИС, перед тем как выставить их на линию DATA0. Это связано с тем, что в соответствии с инструкциями по программированию ПЛИС серии 5576 и 5578, байты конфигурационных данных на линии DATA0 должны передаваться младшим битом вперёд. А у flash-памяти типа К1636РР4У передача байт данных на линии SO - старшим битом вперёд. Для согласования по ориентации направления битов передаваемых байтов на линии DATA0 необходимо осуществить реверс порядка битов в байтах на противоположный. Интерфейсный контроллер MDR_SSP(SPI) микроконтроллера К1986ВЕ92У не имеет возможности менять порядок выдачи битов на линию SO.

- «void sendDataByteFPGA(uint8_t)» служит для передачи байта на линию DATA0 посредством интерфейса SPI микроконтроллера.

Сохранить статью в PDF